# The SOP for Miniaturized, Mixed-Signal Computing, Communication, and Consumer Systems of the Next Decade

Rao R. Tummala, Fellow, IEEE, Madhavan Swaminathan, Senior Member, IEEE,

Manos M. Tentzeris, Senior Member, IEEE, Joy Laskar, Senior Member, IEEE,

Gee-Kung Chang, Senior Member, IEEE, Suresh Sitaraman, David Keezer, Senior Member, IEEE, Daniel Guidotti,

Zhaoran Huang, Kyutae Lim, Lixi Wan, Swapan K. Bhattacharya, Venkatesh Sundaram, Fuhan Liu, and P. Markondeva Raj

Abstract—From cell phones to biomedical systems, modern life is inexorably dependent on the complex convergence of technologies into stand-alone products designed to provide a complete solution in small, highly integrated systems with computing, communication, biomedical and consumer functions. The concept of system-on-package (SOP) originated in the mid-1990s at the NSF-funded Packaging Research Center at the Georgia Institute of Technology. This can be thought of as a conceptual paradigm in which the package, and not the bulky board, as the system and the package provides all the system functions in one single module, not as an assemblage of discrete components to be connected together, but as a continuous merging of various integrated thin film technologies in a small package. In the SOP concept, this is accomplished by codesign and fabrication of digital, optical, RF and sensor functions in both IC and the package, thus distinguishing between what function is accomplished best at IC level and at package level. In this paradigm, IC's are viewed as being best for transistor density while the package is viewed as being best for RF, optical and certain digital-function integration. The SOP concept is demonstrated for a conceptual broad-band system called an intelligent network communicator (INC). Its testbed acts as both a leading-edge research and teaching platform in which students, faculty, research scientists, and member companies evaluate the validity of SOP technology from design to fabrication to integration, test, cost and reliability. The testbed explores optical bit stream switching up to 100 GHz, digital signals up to 5-20 GHz, decoupling capacitor integration concepts to reduce simultaneous switching noise of power beyond 100 W/chip, design, modeling and fabrication of embedded components for RF, microwave, and millimeter wave applications up to 60 GHz. This article reviews a number of SOP technologies which have been developed and integrated into SOP test bed. These are 1) convergent SOP-based INC system design and architecture, 2) digital SOP and its fabrication for signal and power integrity, 3) optical SOP fabrication with embedded actives and passives, 4) RF SOP for high Q-embedded inductors, filters and other RF components, 5) mixed signal electrical test, 6) mixed signal reliability, and 7) demonstration of SOP by INC prototype system.

Index Terms—Antennas, detectors, digital system-on-package (SOP), embedded components, embedded passives, embedded waveguides, electromagnetic interference (EMI), microvia, mixed signal design, optical SOP, power integrity, reliability, RF SOP, signal integrity, SIP, SOP, switches, test.

Manuscript received February 17, 2004; revised March 17, 2004.

The authors are with the Packaging Research Center, School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, GA 30332-0560 USA (e-mail: rao.tummala@ee.gatech.edu).

Digital Object Identifier 10.1109/TADVP.2004.830353

## I. INTRODUCTION

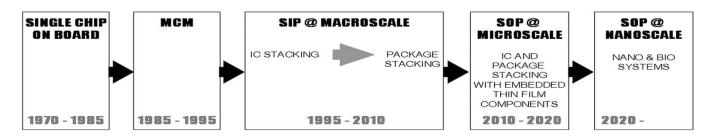

N early 1970s, the single-chip packages on drilled-boards served the needs of the industry. The unparalleled performance needs of mainframes to meet the needs of corporate businesses demanded more integrated systems packaging technologies, giving rise to the birth of "MCM", initially with multilayer ceramic and subsequently with copper-polymer thin films in 1980 [1]. The MCMs, however, have not emerged to be widely accepted for two reasons: high cost, and lack of "Known Good Bare Die". To make it more cost effective, MCM thin-film technology began to be processed on larger boards, leading to build-up or surface laminar circuitry [2]. Even this technology, which is primarily used as thin-film multilayer wiring on packages such as BGAs, has not totally migrated to large-area boards. Independently, the so-called System-on-Chip or SOC became the dream of semiconductor companies in 1990s, depending less and less on packaging because of its high cost, bulkiness, and low performance and reliability. Over the next decade, it became clearer, however, that SOC for a complete system, presents fundamental, engineering, and investment barriers. This is about the time that portable electronics such as cell phones, laptops, PDAs, smart cards, and RF IDs began to emerge as primary consumer systems (see Fig. 1). The systems also began to be convergent, combining computing and communication functions in consumer-sized systems. This led the industry to invent a different MCM called SIP (system-in-package), one that could be stacked with multiple ICs or multiple package-stacked ICs and this time at much lower cost and size [3]. SIP can go one step further in embedding both active and passive components, but passive component embedding is largely of currently available bulky and multilevel thick film discrete components. This distinguishes SIP from SOP in that SOP involves embedding of both active and passives, but the passives are by incorporation of ultrathin films at microscale in the short term and nanoscale in the long term with a goal of increasing component density [4]-[7]. As pointed out in the first paper of this issue, all the above systems packaging technologies have one major shortcoming. They depend primarily on CMOS for the system characteristics and packaging to simply provide interconnections. The CMOS-based evolution and systems packaging evolution to SIP or MCM needed a different approach, one

Fig. 1. Systems packaging has been evolving over decades consistent with systems needs as shown.

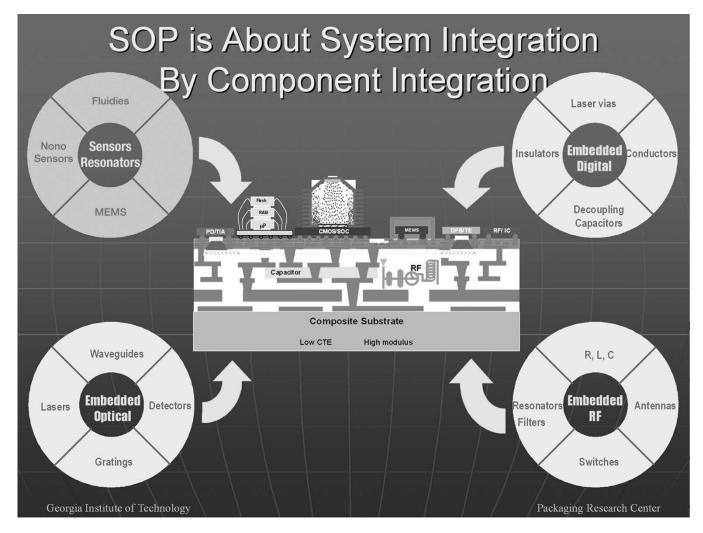

Fig. 2. SOP is about system integration by component integration.

that takes advantage of CMOS for what it is good for-namely transistors, and packaging for what it is good for—namely integration such as RF, Optical and certain digital functions. This is the conceptual paradigm that has become to be known as SOP or System-on-package, proposed by Prof Tummala in October 1993 [8] that led to the formation of the largest academic Center in the United States called the Pakaging Recearch Center (PRC) at Georgia Institute of Technology. In this concept, the package becomes the board and it is not simply for computing but also for communications and perhaps biomedical systems in highly miniaturized systems. This evolution depicting SOP for mixed signal systems based on embedding of components in thin-film form leading to highly miniaturized systems is shown in Fig. 2.

## II. MIXED SIGNAL SOP SYSTEM DESIGN AND ARCHITECTURE

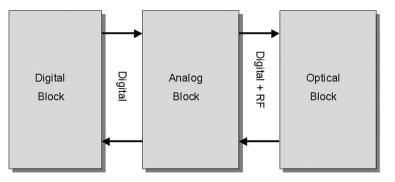

The Georgia Tech's PRC has proposed what it calls an Intelligent Network Communicator (INC) system as a demonstrator of the SOP technology [9]. The INC system is driven by the emerging concepts that the future networks will have to deal with the optical, RF and digital signals in an unique and integrated system with new capabilities in both computing and communications. The INC system, therefore, is composed of three subblocks: the digital, analog, and optical sections, as shown in Fig. 3. Each of the subsystem blocks has been defined to deal with its own barrier issues. Since the entire system is built using a single SOP module platform, interfaces and isolation between

INTELLIGENT NETWORK COMMUNICATOR

Fig. 3. INC system configuration in SOP technology.

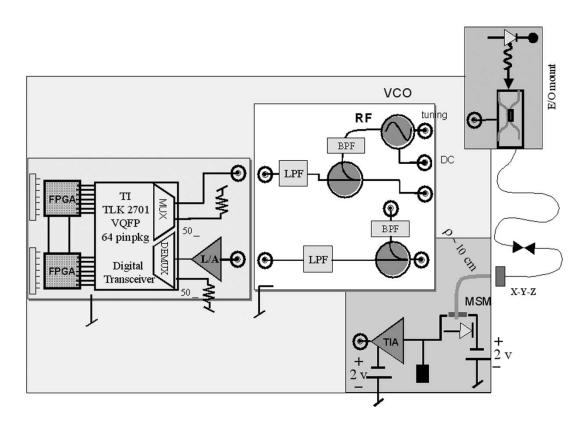

Fig. 4. INC mixed signal system with digital, optical, and RF blocks and interfaces.

the subsystem blocks become very important. The function of the INC is to transmit and receive high-speed digital and modulated RF signals, say wireless signal, concurrently over the optical channel. The system specification of each block has been defined to address the functional integration of that subsection. The target specification of each block in INC is summarized in Table I. The detailed configuration of the proposed system design is presented in Fig. 4. At the digital block, the multigigabit digital signal is generated by using the FPGA and compared with the received-signal after passing through the analog and optical blocks. The digital transceiver converts the multichannel input signals into a single data stream to feed to the analog block. The digital signal is then combined with modulated RF signal and transferred to optical block at the analog block. To accomplish this mission, a custom-designed mixed

TABLE I TARGET GOAL

| Digital<br>Block | Data rate/channel   | 155 Mbps/Channel                |  |  |  |

|------------------|---------------------|---------------------------------|--|--|--|

|                  | Aggregate date rate | 2.5 Gbps (16 Channel)           |  |  |  |

| Analog<br>Block  | Carrier frequency   | 5.8 GHz                         |  |  |  |

|                  | Signal Bandwidth    | Single tone (VCO) / 20MHz (AWG) |  |  |  |

| Optical<br>Block | O/E modulator       | DC ~ 10 GHz (Mach-Zehnder)      |  |  |  |

|                  | Photo Detector      | DC ~ 10 GHz (Embedded)          |  |  |  |

|                  | Light source        | 1530 ~ 1565 nm                  |  |  |  |

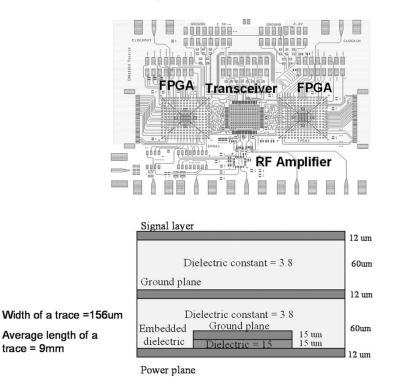

## Layout and Cross Section

Fig. 5. Architecture of digital block. Layout and cross section of digital block.

signal combiner is used for the RF signal. The wireless LAN signal is generated by the electronic generation and a single carrier signal is generated by the voltage controlled oscillator. At the optical block, the mixed signal information is converted to light wave and transmitted through the embedded optical wave-guide or optical fiber. The embedded photodetector converts the optical signal to electrical signal. At the receiver end of the analog block, the electrical signal obtained after passing the photo detector is separated into the digital and RF signals. The FPGA compares the generated-data and received-data to evaluate the system performance. To enable the single packaging solution, the various embedded optical waveguide have been implemented based on low-cost materials and process package technology on 300 mm boards.

#### **III. DIGITAL SOP: DESIGN AND FABRICATION**

The primary goal of any digital system is to ensure maximum throughput between IC's. One example that has plagued the industry for decades is the data path between microprocessors and memory or between multiple cores within a microprocessor. New architectures are being proposed for supporting terabit data rate speeds between processors (such as by Hofstee in this issue [10]. In addition, for memory channel, interconnection speeds greater than 3.2 Gb/s are being developed [11]. For the first time, the International Technology Roadmap on Semiconductors (ITRS) [12] is proposing the convergence of on-chip and off-chip clock speeds, with a goal of 5 GHz clock speed in the near future. These data rates are placing new challenges in the area of signal integrity, power integrity, and electromagnetic interference (EMI) in all systems including in SOP.

These challenges increase exponentially in mixed signal systems that integrate RF front ends with optical signaling and digital base-band processing. Though, the digital circuits operate at a slower speed compared to the predictions by ITRS in mixed signal systems, managing noise becomes a fundamental problem. Hence, along with supporting gigabit data rates on the interconnections, a noise free environment with isolation levels of less than -100 dB are required. This can be a difficult problem to solve, unless integrated technologies with good layout practices and clever architectures are used to minimize coupling. To reduce time to market, modeling tools supporting both prelayout analysis and post-layout verification become an integral part of the design flow. In this section, the design of the digital processing block in the mixed signal system shown previously in Fig. 2 is described in detail with emphasis on layout, modeling, technology integration, and measurements.

## A. Design and Modeling

The physical layout and cross section of the digital block is shown in Fig. 5. The design uses microstrip lines on the top layer for signaling with ground and power plane layers beneath it. The 60  $\mu$ m separation between the power and ground planes, provides for a low impedance path for the power distribution. An additional embedded decoupling layer using a nano-composite material (relative permittivity of 30) with a thickness of 10  $\mu$ m

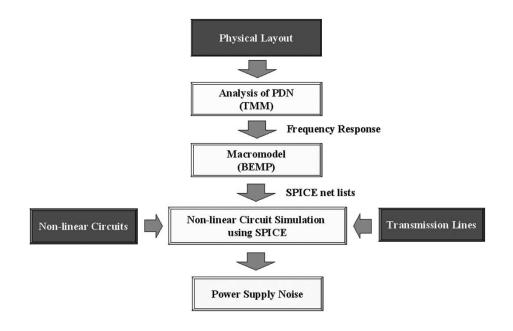

Fig. 6. Design and modeling flow.

enables further lowering of the impedance. This layer, which was patterned to minimize defects, acts as a low impedance path for the decoupling capacitors on the top layer and provides adequate isolation levels for a common power distribution network. The dielectric material used was epoxy (er = 3.8) with copper metallization. The design consists of split power islands to isolate the transmitter and receiver FPGA's from the transceiver chip. Ferrite bead, with an impedance of 600  $\Omega$  at 100 MHz was used to isolate the power planes and provide a common dc potential. A total of thirty-two 0402 decoupling capacitors with capacitance ranging from 1 nF to 47  $\mu$ F were used in the design, to minimize the power supply noise. The microstrip lines with impedance of 50  $\Omega$  were terminated using resistors. A source synchronous design was used by transmitting the clock along with the data on adjacent interconnection.

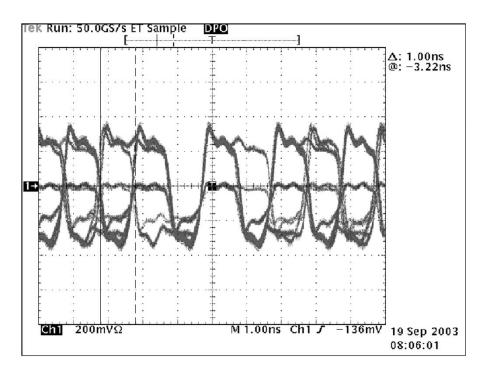

Modeling tools developed at Georgia Tech were used to analyze the design for ensuring signal quality and noise minimization. The design and modeling flow is shown in Fig. 6, where the power distribution network (PDN) was first analyzed using the Transmission Matrix Method (TMM) [13] to extract the frequency response. The frequency response was then approximated using the Broad-band Efficient Macro-modeling Program (BEMP) [14] developed at Georgia Tech, to automatically generate a spice netlist of the power distribution. Nonlinear driver models and transmission lines were connected to the spice model of the power distribution to model the power supply noise. The layout in Fig. 5 was represented as a 14 port circuit for analysis, for extracting the coupling between various parts of the structure. At frequencies beyond 1 GHz, the inductance behavior of the power distribution is considerably reduced with embedded decoupling due to the thin separation between the plates of the capacitor. The time domain response of the power supply noise in the vicinity of FPGA 1 is a  $10 \times$ reduction in noise with embedded decoupling. The transceiver output is shown in Fig. 7, demonstrating the ability to support a 2.48-Gb/s differential serial channel.

### IV. DIGITAL SOP FABRICATION

The digital SOP research focuses on ultrahigh-density wiring and low-loss dielectrics for high-speed signals and thin-film embedded decoupling capacitors for suppression of power noise.

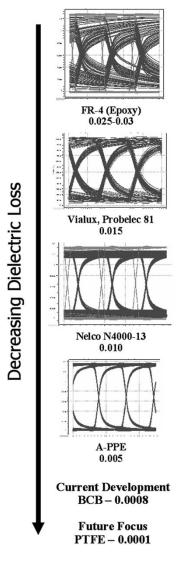

## A. High Speed Wiring and Dieletrics

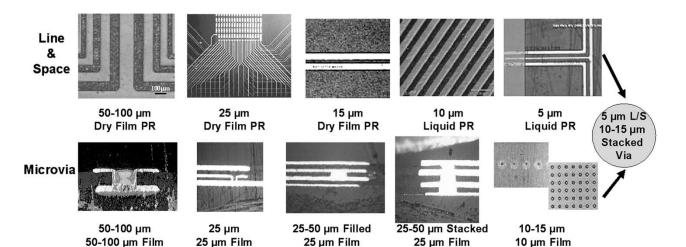

The primary objective of SOP-digital wiring involves the integration of (a) ultralow-loss ( $\sim 0.001$ ) and thin film (5–10  $\mu$ m) polymer dielectrics to achieve signal speeds of >10 Gb/s in the SOP package; and (b) multiple layers of ultrafine lines (5  $\mu$ m) and stacked vias (10–15  $\mu$ m) for wiring density >5000 cm/cm<sup>2</sup> and 50–100  $\mu m$  area array pitch flip chip attach with Wafer Level Packages. The recently released 2003 ITRS roadmap [15] calls for >7.5 GHz package signal speeds and 100  $\mu m$  flip chip pad pitch to satisfy 50 nm node requirements for future ICs. There have been significant developments in microvia and high-density build-up substrates and the state-of-the-art manufacturing processes use  $25 \,\mu m$  line and space technology and 50–75  $\mu$ m microvias [16]–[20]. Several low loss and low k polymers including epoxy, A-PPE, Avatrel, BCB, polyimide, and LCP have been evaluated at the PRC for signal speed and loss at frequencies up to 20 GHz. The typical properties of these materials are shown in Table II. The impact of dielectric loss on the signal speed is shown in Fig. 8 using measured eye diagrams at 5 Gb/s for low-loss polymers. For future SOP applications, thin film (10–15  $\mu$ m) build-up dielectrics like BCB will enable the design of 50  $\Omega$  signals using 10  $\mu$ m lines and spaces. The ideal dielectric for build-up SOP will combine the low loss of PTFE ( $\sim 0.0001$ ) for high speed with ultrathin-film processing for maximum interconnect density.

Area array I/O pitch of 50–100  $\mu$ m requires escape routing with 5–10  $\mu$ m lines and spaces and 10–15  $\mu$ m stacked microvias. These dimensions have recently been demonstrated on low cost build-up PWB core substrates. Fig. 9 includes an extremely fine structure with 5 and 10  $\mu$ m wide lines, 10  $\mu$ m

Fig. 7. 1. 6 Gb/s transceiver output.

TABLE II

PROPERTIES OF LOW-LOSS POLYMERS AT 1 GHz

| Dielectric | Dielectric Constant | Tan δ      |

|------------|---------------------|------------|

| Ероху      | 3. 8-4. 5           | 0.015-0.03 |

| PPE        | 3.2                 | 0.005      |

| LCP        | 2.8                 | <0.003     |

| Polyimide  | 3. 3-3. 5           | 0.005      |

| Avatrel    | 2.5                 | <0.001     |

| BCB        | 2.9                 | <0.001     |

spaces, and 4  $\mu$ m copper thickness. Precision photolithography with negative-acting liquid photoresists, glass photomasks and semi-additive plating processes were used to form these structures. A novel low-cost process for fabricating planar multilayer wiring with stacked microvias without any CMP process has been demonstrated. Fig. 9 includes a four metal layer of such a stacked via structure with fully filled copper studs of 50  $\mu$ m diameter [21].

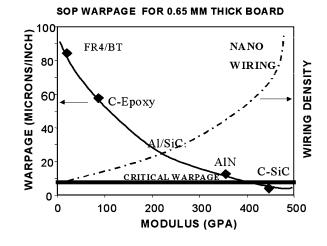

Packages for sub  $-100 \ \mu m$  area array pitch, without large capture pads, require substrates with exceptional dimensional stability and high modulus to prevent warpage during multilayer thin film build-up. Fig. 10 summarizes the substrate warpage requirements needed to support ultrahigh wiring density and sufficient flatness for fine pitch assembly. Novel C-SiC large-area boards are being developed with CTE as low as 3–5 ppm/C and modulus as high as 450 GPa [22]. Such a material with exceptional dimensional stability will enable much tighter layer-to-layer registration and higher pad density. The CTE-match to Si

is expected to help immensely to minimize stress on the solder joint and perhaps may eliminate expensive underfill processing.

## B. Power Integrity by Embedded Decoupling Dielectrics

Embedded high-k dielectrics are particularly useful as midfrequency decoupling capacitors for reducing ground bounce and simultaneous switching noise. Current surface mount discrete components are expected to reach their limit of operation in the few hundred MHz range due to the high lead inductance associated with solder interconnects. Novel polymer-ceramic nanocomposite dielectrics [23] have been used to fabricate thin film capacitors with a thickness of 10  $\mu$ m and  $\varepsilon$  of 30 to achieve capacitance density up to 2.6 nF/cm<sup>2</sup>. Noise levels below 90 mV peak-to-peak have been demonstrated with this approach.

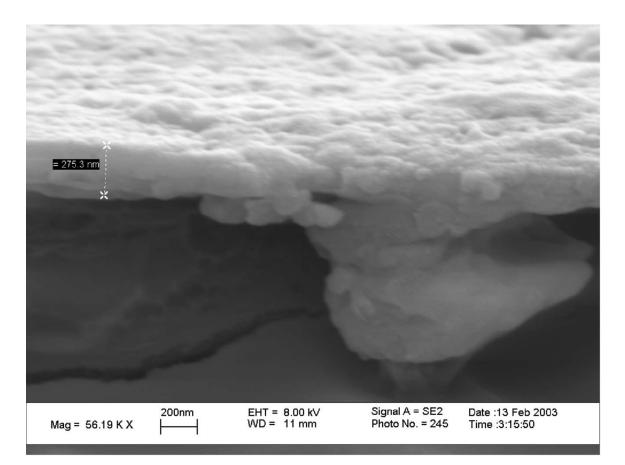

To achieve noise levels below 50 mV and to support power levels above 200 W, ultrathin-film high-k dielectrics are being developed using novel low temperature processes. Such synthesis methods as hydrothermal and sol-gel, with rapid thermal processing, have demonstrated films with thickness  $<1 \,\mu\text{m}$  and capacitance densities of about 500 nF/cm<sup>2</sup>. The low process temperatures below 200 °C are well suited for integration on low cost organic SOP substrates. Fig. 11 shows a top view of a dense BaTiO<sub>3</sub> film fabricated on metal foil using hydrothermal synthesis [24].

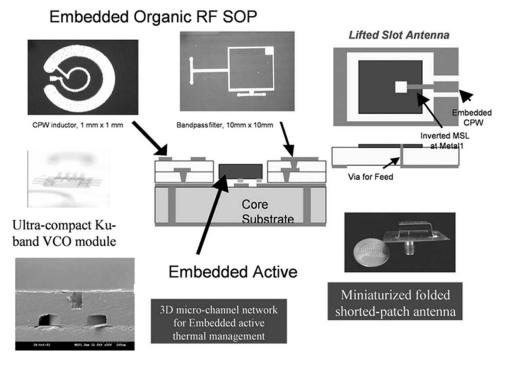

## V. ORGANIC RF SOP

The SOP is a single component, multifunction package solution providing the needed system functions that include analog, digital, RF, optical and MEMS. The SOP also allows efficient integration of complete passive RF front-end functional building blocks, such as filters and power combiners. Recent development of thin-film RF materials and processes makes it possible to bring the concept of SOP into the RF world to meet

Fig. 8. Impact of dielectric loss on signal integrity for various thin-film materials (eye diagrams at 5 Gb/s).

the stringent needs in wireless communication area [25]–[28]. Critical issues such as wideband and low-loss interconnects, high-Q multilayer passives including R, L and C's [29]–[32], board-compatible embedded antennas and switches [33]–[35], low-loss and low-cost boards, efficient partitioning of MMICs, low crosstalk embedded transmission lines and single-moded packages, as well as design rules for vertically integrated transceivers are major barriers that have to be addressed over a wide frequency range. In addition, there exists a gap in the area of hybrid CAD needed to model novel functions that require fast and accurate modeling of electromagnetic, circuit, solid-state, thermal and mechanical effects.

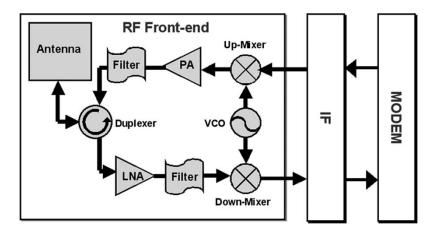

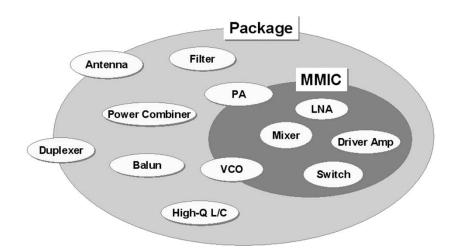

Multilayer ceramic (LTCC) and multilayer organic (MLO) structures with liquid crystal polymer (LCP) technology [32] are used to embed passives efficiently, including high-Q inductors, capacitors, matching networks, low-pass and band-pass filters, baluns, combiners, and antennas. The 3-D design approach using multilayer topologies leads to high quality and compact components to support multiband, wider-bandwidth and multistandards in a very compact from factor and with low cost. A general system configuration of wireless transceiver is shown

in Fig. 12. The breadth of integration is represented schematically in Fig. 13. The Transceiver module is composed of MMIC chipset: power amplifier (PA), low-noise amplifier (LNA), up and down mixer (MIX) and voltage controlled oscillator (VCO), and passive components: filter, antenna, and external high-Q discrete passive elements for stringent block such as PA and VCO. Some examples of passives built on SOP platform are represented in Fig. 14.

## A. Multilayer Inductors

High-Qs at the frequency range of interest can be obtained by designing CPW inductors using multilayer organic technology. The CPW spiral inductor, depicted in Fig. 14, avoids via losses, has reduced dielectric losses and increased SRF. Also, the thick copper metallization in the packaging process make it possible to get a very high-Q. This decreases the shunt parasitic capacitance and reduces the eddy current flowing in the ground plane producing negative mutual inductance effect. As a result, higher Q and  $L_{\rm eff}$  can be achieved. The CPW inductor demonstrates a Q of 182, SRF 20 GHz, Leff 1. 97 nH.

## B. Embedded Filters

Several embedded filters were designed for the SOP process using epoxy materials for the build-up layers. The bandpass filter design for C band applications consists of a square patch resonator with inset feed lines, as shown in Fig. 14. The inset gaps act as small capacitors and cause the filter to have a pseudoelliptic response with transmission zeros on either side of the passband. This structure also has a tunable bandwidth. The length of the feed lines is determined by the input and output matching requirements. The length of the insets and the distance between them are the main controlling factors, effectively setting the size of the mode-splitting perturbation in the field of the resonator. Measurement result shows that bandwidth of 1.5 GHz and a minimum insertion loss of 3 dB at the center frequency of 5.8 GHz.

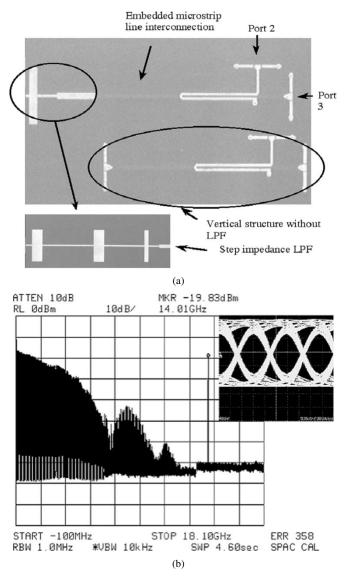

## C. Combiners

To overcome the weak coupling at base band and the bandwidth limitation of conventional combiner, we modified the conventional coupled line coupler as vertical coupling structure in the SOP platform as shown in Fig. 15(a). The output port of the coupled line coupler is used as the input port for the RF signal and the isolation port is shorted to the ground. Also we designed ninth-order Bessel LPF at the input port for the base band, which performs as band stop filter for the 14 GHz RF signal and reflects the RF signal at the output of the LPF. We optimized the 14 GHz RF signal in-phase to obtain a constructive effect at the output port of the combiner by adjusting the embedded microstrip line which interconnects the LPF with vertical coupling structure. The design was finalized with the 3-D electromagnetic simulation software. The insertion loss of the RF signal at the output port of the combiner was measured as 1.9 dB. The isolation between port 1 and port 2 of the combiner was greater than 10 dB in base band and 38 dB at 14 GHz (VNA HP8510). These results satisfy the requirement for the proposed HDROS. 3 dB bandwidth of 7 GHz is achieved between port 1

Fig. 9. Progress in lines and spaces, and microvias on low-cost organic SOP substrates at PRC.

Fig. 10. SOP substrate warpage requirements for 0. 65 mm thickness.

and port 3. Fig. 15(b) shows the measured frequency spectrum at the output of the combiner when 7 Gb/s pseudorandom binary sequence (PRBS) with 14 GHz sinusoidal wave are sent. Fig. 15(b) also shows the measured eye opening of the 7 Gb/s PRBS at the output port.

## D. Antennas

SOP can give flexibility to the transceiver module by integrating all functional blocks using the multilayer processes and the novel interconnection methods. One of the major issues, however, is how to integrate antennas with a high module efficiency and low cost, especially for the lowest frequencies of cellular communication and WiFi, that the physical antenna size is large. Fabricating an antenna directly on the package has the advantages of reduced feeder loss and size of the entire module. For the frequency band of the personal communication, WLAN and short-range broadband communications from 900 MHz to 6 GHz and 35-65 GHz, it is difficult to put an antenna into the module, since the size of the antenna becomes large. Moreover there are issues to be solved such as narrow bandwidth in ceramic packaging and interference between the antenna and other RF blocks in highly integrated module. The prototype antennas are designed to be integrated with the transceiver module and fabricated using multilayer package processes, such as MLO and LCPs [36]. The principle of novel soft–hard surfaces (SHS) was devised for the miniaturization and elimination of the substrate-crosstalk modes improving the efficiency of higher patch antennas [34] close to the free-space ones and suppressing the backside radiation by 10–15 dBs from 900 MHz and 1.55 GHz (GPS) to the short-range broadband (40–65 GHz). In addition, stacked-patch configurations allowed for the realization of broadband radiation performances.

## E. Capacitors

Embedded high-k polymer/ceramic nanocomposite capacitors (dielectric constant 15–20) have been used primarily for the decoupling applications as discussed earlier. Currently, a capacitance density ~1  $\mu$ F/cm<sup>2</sup> has been reported with a thin film of BaTiO<sub>3</sub> using hydrothermal synthesis [37] that can be integrated with the SOP. Dielectric constant >1000 has been reported using metallic nanoparticles [38].

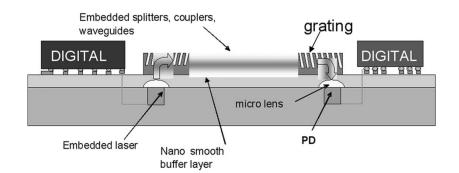

### VI. OPTOELECTRONICS SOP

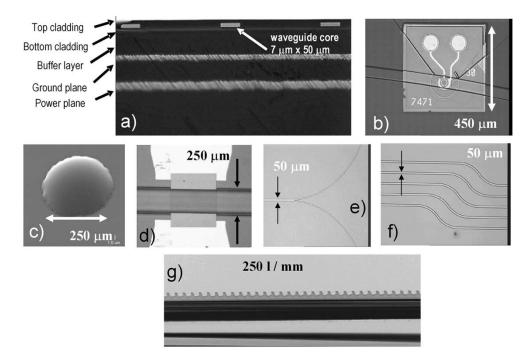

The focus of Optoelectronics SOP is the heterogeneous integration of optically active devices such as lasers, detector arrays, and laser amplifiers, and optically passives such as waveguides, gratings and beam splitters onto electrically interconnected mixed signal SOP, as shown in Figs. 16 and 17.

#### A. Integration of Embedded Active Optical Elements

The metal–semiconductor–metal photodetector (MSM-PD) has attracted attention from industry in recent years because of its simplicity in fabrication, lower capacitance than p-i-n photodiodes per unit area, and high alignment tolerance for assembly. In this research, the MSM-PD is independently grown, fabricated, and bonded directly onto organic boards and silicon chips. MSM-PDs are fabricated on an  $In_{0.53}Ga_{0.47}As$  layer which is grown on lattice-matched InP. The absorbing layer thickness can be varied between 100 and 740 nm to achieve the optimized responsivity and bandwidth [39], [40]. The Schottky electrode comb structure is patterned by standard photolithography and metallized with Ti/Pt/Au using e-beam evaporator. The InP growth substrate is removed by chemical etching, leaving a thin

Fig. 11. SEM cross section of high K(> 350) hydrothermally grown film of BaTiO<sub>3</sub>.

Fig. 12. RF transceiver architecture.

film device with a thickness of  $\sim 1 \ \mu m$ . Each individual PD is picked and inversely bonded onto the host substrates. Thus, the responsivity of the inverted MSM (I-MSM) is improved significantly by eliminating the electrode shadowing effect [41]. The low temperature organic board is pretreated with a planarizing polymer buffer layer and the metal contact pads are sputtered or evaporated on the lower waveguide cladding. The pads are used to either bump-bond with electronic chips or bond directly to the I-MSM-PDs via Van der Waals attraction. Waveguide polymer material is spin-coated directly onto the SOP substrate and photolithographically patterned into the waveguide structure. As shown in Fig. 16, the optical signals propagate along the polymer waveguide and are diffracted by grating couplers to a PD array. Alternatively, the PDs are evanescently coupled to embedded I-MSMs or p-i-n's, as shown in Fig. 17. The evanescent coupling efficiency from the waveguide to a p-i-n is measured to be 3% at 1.3  $\mu$ m and 1.55  $\mu$ m [42]. In this way, high speed chip to chip data communication on SOP is realized through the optical devices of photodetectors, waveguides, gratings and other optical components. The bandwidth of the PD/waveguide optical interconnect is primarily dominated by the speed of the photodetector.

Fig. 13. RF component integration in IC and SOP package.

Fig. 14. Components fabricated on organic SOP.

#### B. Integration of Optical Passives

The primary focus of embedded passives is process and materials for the fabrication of waveguides, gratings, lenses, couplers and switches on low temperature FR-4 boards. The fabrication process itself presents four main issues: 1) Surface roughness of the organic board, 2) interface adhesion, 3) intrinsic and extrinsic waveguide losses, and 4) reliability. Two materials were used in this study: BCB and Siloxane. Suzuki *et al.* [43] reports a surface roughness of  $\pm 0.2 \,\mu$ m over a distance of 5000  $\mu$ m after BCB planarization of a high  $T_{\rm g}$  FR-4 board. In another paper in this issue, Chang [42] reports an average surface roughness of 4 nm over 5  $\mu$ m and  $\pm 20 \,$  nm over 500  $\mu$ m for a low temperature board planarization process. Although few researchers report on interface adhesion, photo-definable Siloxane-based waveguides passed the "Scotch tape" vertical pull test. The optical loss at 1300 nm for BCB waveguides, prepared by RIE,

is reported to be 0.36 dB/cm [44], consistent with other reports in the literature. For an Ultem(core)/BCB(cladding) waveguide, prepared by RIE, the reported loss [45], [46] is 1.34 dB/cm at 1330 nm. A photodefinable, epoxy-based Siloxane Oligomer had a measured optical loss of 1.43 dB/cm at the same wavelength [42], and a second photodefinable polymer had a measured loss of 0.2 dB/cm at 1330 nm [42]. Reliability issues such as thermal cycling and accelerated optical aging are seldom reported. An array of 5 waveguides composed of epoxy-based Siloxane Oligomer (Polyzet, Inc., New York) on FR-4 boards were cycled between -55 °C and 125°C. Each waveguide is 5 cm long, and all had a cross section of 50  $\mu$ m × 7  $\mu$ m. After 300 cycles, no measurable change in absorption at the two wavelengths was observed in each of five waveguides in an array. Accelerated optical aging test is ongoing. Fabrication and integration technologies are being developed for micro lenses, micro mirrors, switches and couplers, as well as wavelength pro-

Fig. 15. (a) Picture of fabricated combiner in MLO process, 5 mm in length. (b) Frequency spectrum at the output port.

cessing components such as gratings, photonic crystals, arrayed waveguide gratings, multimode interference. Recent global developments in this area can be found elsewhere in this issue [42].

### VII. MIXED-SIGNAL SOP TEST RESEARCH

The PRC research program in mixed-signal test develops electrical functionality validation and performance screening methods for SOP-based systems that include not only high-performance (multigigabits per second) digital signals, but also RF, analog, and optical signals. The research provides cost-effective means to verify functionality and performance in complex "mixed-signal" SOP systems. The Mixed-signal Test research effort is a system level approach that incorporates design-for-test (DFT) and built-in self-test (BIST) features within the SOP design as well as external instrumentation and novel methods for applying tests. To accomplish these, the Systems Test Research involves three areas: 1) design of a high-speed digital test support processor (TSP) for application of multigigahertz tests at the SOP and IC levels [47]–[49]; 2) development of test methods for embedded interconnect and mixed digital/optical signals [48], [49]; and 3) design-for-test methods for Built-In Test of Embedded Mixed-Signal Electronics [50], [51]. The first two research areas share the use of a "Test Support Processor" TSP and are summarized in Section VII-A and the third research area addresses the testing complexities encountered in SOP systems with mixed RF, linear, and digital technologies as outlined below.

## A. Test Support Processor for High-Speed Digital and Mixed Digital/Optical Signals

Even though existing digital devices support I/O data rates in excess of 2 Gb/s, current automated test equipment (ATE) is typically limited to speeds of about 1. 0 to 1. 6 Gb/s (per channel). Furthermore, these high-end systems are expensive, costing \$5 k to \$10 k per channel. The capital cost for a fully populated ( $\sim 1000 \text{ pin}$ ) system can be close to \$10 M. Timing accuracy in these systems is also limited to about 50-100 ps, and random jitter is typically 6 ps to 10 ps. Evolution of ATE is extending data rates to 3. 2 Gb/s and above, and optical bit error rate test (BERT) up to 10 Gb/s and above per channel. One of the most difficult barriers to achieving these goals is the extremely precise timing requirement, inherent to testing high-speed signals. Specifically, there is a need to produce much lower-cost, high-speed (multigigahertz) test channels with low jitter (<2 ps RMS) and timing accuracy of 10 to 20 ps. Required bit error rates (BERs) of  $10^{-12}$  require consideration of 14-sigma jitter tolerance. Integration of high-speed optical components, and mixed digital/RF within the low-cost digital embedded test electronics poses significant technical and economic challenges.

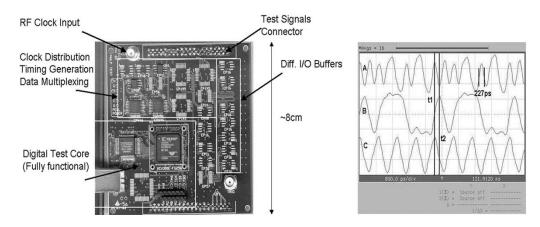

To address these testing requirements, the PRC research program has developed the concept of a Test Support Processor (TSP). In this approach, the conventional ATE is supplemented with customized electronics that provide specialized test functions tailored for a specific SOP. The prototype designs use a field-programmable gate array (FPGA) and a microcontroller as a "Digital Test Core" (see Fig. 18). The FPGA is reprogrammed to supplement the built-in self test (BIST) features of the SOP. The microcontroller provides a communications port (USB) to a personal computer (which is used to control the testing process). Surrounding the Digital Test Core, is customized high-speed logic that is typically needed to multiplex to higher data rates than can be generated by the FPGA alone. In the example of Fig. 18, this logic is implemented using PECL devices capable of operating to about 5 Gb/s. This example TSP provides multiple 5 Gb/s data sources and receivers for testing nanowafer level packaged IC's. It has been adapted from earlier designs that used the same Digital Test Core. Current efforts are centered on extending beyond 5 Gb/s. In a recent design modification, SiGe logic is used for higher bandwidth and provisions to connect optical transceivers have been added.

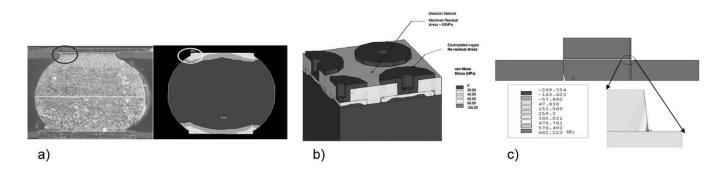

## VIII. MIXED-SIGNAL SOP RELIABILITY

The mixed-signal reliability research focuses on the reliability of individual digital, optical, and RF functions as well as

Fig. 16. Optoelectronic SOP chip-to-chip concept and design.

Fig. 17. Optical component technologies embedded in SOP. (a) Waveguide array embedded in FR-4 board, (b) embedded commercial p-i-n detector, (c) polymer microlens, (d) embedded i-MSM, (e) beam splitter, (f) curved waveguide array, (g) blazed polymer grating, blaze angle 29°.

Fig. 18. Test support processor (TSP) prototype, and 4. 4 Gb/s signal output.

the interface between these functions. For digital function reliability, failure mechanisms such as microvia and global interconnect fatigue failure, dielectric cracking and delamination, die-tosubstrate solder interconnect fatigue failure, underfill cracking and delamination, etc., are being studied through physics-based predictive models, and the onset of such failure mechanisms is linked to digital function degradation and reliability. Similarly, optical loss in waveguides, refractive index stability, misregistration tolerance, bandwidth limitations as a function of distance, stress-optical effects, and waveguide delamination are being modeled to predict the optical function reliability. Similarly, the changes in inductance, capacitance, and resistance of

Fig. 19. Reliability prediction models: (a) solder interconnect, (b) microvia, and (c) interlayer delamination.

| Digital<br>20 410 Ohns Before Bernall Agring | RF After 100 cycles |       |       |              |              | Silicon<br>0.5mm<br>Optical<br>Opto Cross-section |               |                |                  |

|----------------------------------------------|---------------------|-------|-------|--------------|--------------|---------------------------------------------------|---------------|----------------|------------------|

| Z0 = 45.8 Ohms after thermal cycling         | Cap                 | L     | R     | Сар          | L            | R                                                 | Material      | Before thermal | After 100 cycles |

| g **                                         | 28.3pF              | 315mH | 125kΩ | 26.7pF (-4%) | 263mH (-20%) | 110kΩ (-12%)                                      |               | cycling        |                  |

| 3                                            | 37.5pF              | 321mH | 350kΩ | 35.7pF(-4%)  | 263mH (-19%) | 342kΩ (-2%)                                       | Siloxane Core | 1.5104         | 1.5106 (+0.01%)  |

|                                              | 59.6pF              | 220mH |       | 56.8pF(-4%)  | 183mH (-18%) |                                                   | Siloxane      | 1.5455         | 1.5458 (+0.02%)  |

|                                              | 73.7pF              | 222mH |       | 70.1pF(-4%)  | 188mH (-16%) |                                                   | Cladding      |                |                  |

Fig. 20. Experimental tests to assess individual function reliability.

integral passives with thermal excursions and exposure to environmental conditions are being studied with respect to RF functions. In conjunction with the physics-based models, reliability experiments using individual-function testbeds as well as mixed-signal testbeds are being carried out to validate the models and to enhance the modeling methodologies.

Fig. 19 shows some of the predictive modeling results and Fig. 20 shows some of the experimental data used to validate the predictive models. For more details on the models, experimental reliability tests, and material characterization techniques, please refer to [52]–[61].

In a multi-functional system like in SOP, the digital, optical, and RF functions are inter-related, and therefore, in addition to individual function reliability, the interaction effects should also be studied. For example, 1) the presence of high-performance digital function in proximity to a high flux optical domain could overheat the optical waveguides and affect the waveguide reliability, 2) the processing of low-loss interlayer dielectric to achieve digital function target parameters could adversely affect the reliability of the embedded passive layers fabricated, and 3) the warpage introduced due to the processing of different layers and due to the operation of different functions would adversely affect dielectric reliability, waveguide misregistation and optical fidelity, and passive layer adhesion. Therefore, such interaction effects of various functions are being addressed in the system-level reliability models. Development of such system-level reliability models with multiple functions and failure mode interactions requires tremendous computational resources and time. Innovative modeling techniques augmented with high performance computing are being used to ease

Fig. 21. INC-SOP system fabricated with embedded digital, optical, and RF mixed signal functions.

the computational complexity and reduce the time needed in achieving acceptable results. In addition, statistical reliability considerations are also being pursued when addressing the system-level reliability.

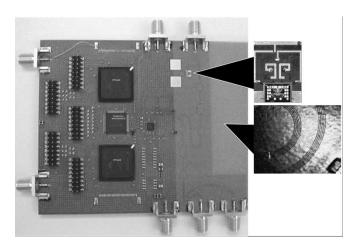

## IX. SOP TECHNOLOGY DEMONSTRATION BY INC SYSTEM PROTOTYPE

The INC system design and architecture has been successfully fabricated, as shown in Fig. 21 by SOP designs and processes, described above. The prototype system was tested at the each of sub-system blocks such as at RF, digital and optoelectronics. The INC system successfully demonstrated digital throughput up to 3.6 Gb/s. Optical link data rates in excess of 10 Gb/s, including butt coupling interconnection between optical waveguide and optical fiber. A VCO has been developed and fabricated as part of this INC prototype, using a MESFET process. To reduce the phase noise of the VCO, which is critical in the multi-carrier modulation, the high-Q embedded inductors are built on the SOP package directly. The RF signal generated by VCO with embedded inductor showed -110 dBc at 6 MHz offset frequency and -10 dBm of output power. After verifying at the sub-system levels, the overall system has been set up on an optical table to prevent unwanted vibration from the embedded optical waveguide interconnection. The demonstration included the signal generated by FPGA combining with RF single carrier signal with optically-modulated signal by MZ modulator. The optical signal was transmitted through the optical fiber and embedded optical waveguide, and then converted into the electrical signals. The system demonstration details can be found elsewhere [62], [63].

#### REFERENCES

- R. R. Tummala et al., Ceramic Packaging Technology, Microelectronics Packaging Handbook. New York: Van Nostrand, 1988.

- [2] Y. Tsukada, S. Tsuchida, and Y. Mashimoto, "Surface laminar circuit packaging," in *Proc. 42nd Electronic Components and Technology Conference*, 1992, pp. 22–7.

- [3] Y. Yano, T. Sugiyama, S. Ishihara, Y. Fukui, H. Juso, K. Miyata, Y. Sota, and K. Fhjita, "Three dimensional very thin stacked packaging technology for SiP," in *Proc. 52nd Electronic Components and Technology Conference*, 2002.

- [4] R. Tummala, "SOP: Microelectronic systems packaging technology for the 21st century," Adv. Microelectron., vol. 26, no. 3, pp. 29–37, May–June 1999.

- [5] R. Tummala, G. White, V. Sundaram, and S. Bhattacharya, "SOP: The microelectronics for the 21st century with integral passive integration," *Adv. Microelectron.*, vol. 27, pp. 13–19, 2000.

- [6] R. Tummala and V. Madisetti, "System on chip or system on package," *IEEE Design Test Comput.*, vol. 16, no. 2, pp. 48–56, Apr.–June 1999.

- [7] R. Tummala and J. Laskar, "Gigabit wireless: System-on-a-package technology," *Proc. IEEE*, vol. 92, pp. 376–387, Feb. 2004.

- [8] R. R. Tummala, "Low Cost and Highly Integrated Systems Packaging," Proposal for NSF Engineering Research Center, 1993.

- [9] K. Lim, M. F. Davis, M. Maeng, S. Pinel, L. Wan, L. Laskar, V. Sundaram, G. White, M. Swaminathan, and R. Tummala, "Intelligent network communicator: Highly integrated system-on-package (SOP) testbed for RF/digital/opto applications," in *Proc. 2003 Electronic Components and Technology Conference*, pp. 27–30.

- [10] H. P. Hofstee, "Future microprocessors and off-chip SOP interconnect," *IEEE Trans. Adv. Packag.*, vol. 27, pp. 65–69, May 2004.

- [11] J. Choi and M. Swaminathan, "Modeling of power supply noise in large chips using the finite difference time domain method," IEEE Trans. Electromagn. Compat., vol. 45, July 2003, submitted for publication.

- [12] International Technology Roadmap on Semiconductors (ITRS). [Online]. Available: www.src.org

- [13] J. H. Kim and M. Swaminathan, "Modeling of multilayered power distribution planes using transmis-sion matrix method," *IEEE Trans. Comp. Packag. Manufact. Technol.*—*Adv. Packag.*, vol. 25, no. 2, pp. 189–199, May 2002.

- [14] S. H. Min and M. Swaminathan, "Construction of broadband passive macromodels from frequency data for simulation of distributed interconnect networks," in *Proc. Int. Symposium on Electromagnetic Compatibility*, Zurich, Switzerland, Feb. 2003.

- [15] "International Technology Roadmap for Semiconductors, 2003 Edition "Assembly and Packaging"," Semiconductor Industry Association, Chapter, Table 92a, 92b, 96, 100, 2004.

- [16] V. Sundaram, R. Tummala, F. Liu, P. Kohl, J. Li, S. A. Bidstrup-Allen, and Y. Fukuoka, "Next generation microvia and global interconnect technologies for SOP," IEEE Trans. Adv. Packag., 2004, submitted for publication.

- [17] M. Asai, "New packaging substrate technology IBSS (interpenetrating polymer network build up structure system)," in *Proc. Electronic Packaging Materials Science IX. Symposium*, 1997, pp. 117–24.

- [18] K. Segawa, "Build-up PWB with laser-processed via holes "VIL"," Proc. SPIE—The International Society for Optical Engineering, vol. 3582, pp. 419–24, 1999.

- [19] D. Andoh, Y. Tomita, T. Nakamura, and F. Echigo, "The progress of the ALIVH substrate," in *Proc. 52nd Electronic Components and Tech*nology Conference, 2002, pp. 1419–24.

- [20] T. Kariya and R. Enomoto, "Development of multilayer printed wring board with stacked via holes using single step laminating process," in *Proc. 3rd IEMT/IMC Symposium*, 1999, pp. 194–199.

- [21] F. Liu, G. White, V. Sundaram, A. O. Aggarwal, S. M. Hosseini, D. Sutter, and R. Tummala, "A novel technology for stacking microvias on printed circuit boards," in *Proc. 53rd IEEE ECTC*, May 2003, pp. 1134–1139.

- [22] N. Kumbhat, P. M. Raj, R. Pucha, S. Sitaraman, V. Sundaram, S. Bhattacharya, R. Tummala, S. Hayes, and S. Atmur, "Next generation of package/board materials technology for ultra-high density wiring and fine-pitch reliable interconnection assembly," in *Proc. Electronic Components and Packaging Technology Conference*, Las Vegas, NV, 2004.

- [23] J. Hobbs, H. Windlass, V. Sundaram, S. Chun, M. Swaminathan, and R. Tummala, "Simultaneous switching noise suppression for high speed systems using embedded decoupling," in *Proc. 51st ECTC Conference*, Orlando, FL, May 2001.

- [24] D. Balaraman, P. M. Raj, S. K. Bhattacharya, and R. Tummala, "Novel hydrothermal processing of ceramic-polymer composites for integral capacitor applications," in *Proc. Electronic Components and Technology Conference*, San Diego, CA, May 2003, pp. 1699–1703.

- [25] M. F. Davis, A. Sutono, A. Obatoyinbo, S. Chakraborty, K. Lim, S. Pinel, J. Laskar, and R. Tummala, "Integrated RF architectures in fully-organic SOP technology," in *Proc. 2001 IEEE EPEP Topical Meeting*, Boston, MA, Oct. 2001, pp. 93–96.

- [26] K. Lim, A. Obatoyinbo, M. F. Davis, J. Laskar, and R. Tummala, "Development of planar antennas in multi-layer package for RF-system on-a-package applications," in *Proc. 2001 IEEE EPEP Topical Meeting*, Boston, MA, Oct. 2001, pp. 101–104.

- [27] M. F. Davis, A. Sutono, K. Lim, J. Laskar, V. Sundaram, J. Hobbs, G. E. White, and R. Tummala, "RF-Microwave multi-layer integrated passives using fully organic system on package (SOP) technology," in *Proc. IEEE International Microwave Symposium*, vol. 3, Phoenix, AZ, May 2001, pp. 1731–1734.

- [28] M. F. Davis, A. Sutono, K. Lim, J. Laskar, and R. Tummala, "Multilayer fully organic-based system on package (SOP) technology for RF applications," in *Proc. 2000 IEEE EPEP Topical Meeting*, Scottsdale, AZ, Oct. 2000, pp. 103–106.

- [29] J. M. Hobbs, S. Dalmia, V. Sundaram, L. Wan, W. Kim, G. White, M. Swaminathan, and R. Tummala, "Development and characterization of embedded thin-film capacitors for mixed signal applications on fully organic system-on-package technology," in *Proc. IEEE 2002 Radio and Wireless Conference, RAWCON 2002*, Aug. 11–14, 2002, pp. 201–204.

- [30] R. Ulrich and L. Schaper, "Decoupling with embedded capacitors," *CircuiTree*, vol. 16, no. 7, pp. 26–26, July 2003.

[31] A. Murphy and F. Young, "High frequency performance of multi-

- [31] A. Murphy and F. Young, "High frequency performance of multilayer capacitors," *IEEE Trans. Microwave Theory Tech.*, vol. 43, pp. 2007–2015, Sept. 1995.

- [32] R. Ulrich and L. Schaper, Eds., Integrated Passive Component Technology: IEEE Press/Wiley, 2003.

- [33] J. Laskar, M. Tentzeris, K. Lim, S. Pinel, M. Davis, A. Rhagavan, M. Maeng, S.-W. Yoon, and R. Tummala, "Advanced system-on-Package RF front-ends for emerging wireless communications," in *Proc. 2002 Asian-Pacific Microwave Symposium*, Kyoto, Japan, Nov. 2002, pp. III. 1703–1708.

- [34] R. L. Li, G. DeJean, M. M. Tentzeris, and J. Laskar, "Integration of miniaturized patch antennas with high dielectric constant multilayer packages and soft-and-Hard surfaces (SHS)," in *Proc. 2003 IEEE-ECTC Symposium*, New Orleans, LA, May 2003, pp. 474–477.

- [35] R. L. Li, K. Lim, M. Maeng, E. Tsai, G. DeJean, M. Tentzeris, and J. Laskar, "Design of compact stacked-patch antennas on LTCC technology for wireless communication applications," in *Proc. 2002 IEEE AP-S Symposium*, San Antonio, TX, June 2002, pp. II. 500–503.

- [36] D. Thompson, P. Kirby, J. Papapolymerou, and M. M. Tentzeris, "W-Band characterization of finite ground coplanar transmission lines on liquid crystal polymer (LCP) substrates," in *Proc. 2003 IEEE-ECTC Symposium*, New Orleans, LA, May 2003, pp. 1652–1655.

- [37] D. Balaraman, P. M. Raj, I. Abothu, S. Bhattacharya, S. Dalmia, L. Wan, M. Swaminathan, and R. Tummala, "Integration and high-frequency characterization of PWB-compatible pure barium titanate films synthesized by modified hydrothermal techniques below 100°C," in *Proc. 53rd Electronic Components and Technology Conference*, New Orleans, LA, May 2003, pp. 1520–1527.

- [38] Y. Rao, J. Yue, and C. P. Wong, "Materials characterizations of high dielectric constant polymer-ceramic composite for embedded capacitor for RF application," *Active Passive Elec. Comp.*, vol. 25, pp. 123–129, 2002.

- [39] Z. Huang, C. Cha, S. Chen, J. J. Shen, N. Jokerst, M. Brooke, and A. Brown, "InGaAs MSM photodetector modeling using DOE analysis," *Proc. SPIE*, vol. 5178, pp. 148–156, 2003.

- [40] Z. Huang, Y. Ueno, K. Kaneko, N. M. Jokerst, and S. Tanahashi, "Embedded optical interconnections using thin film InGaAs MSM photodetectors," *Electron. Lett.*, vol. 38, pp. 1708–1708, 2002.

- [41] J. Kim, H. T. Griem, R. Friedman, E. Chan, and S. Ray, "High-performance back-illuminated InGaAs/InAlAs MSM photodetector with a record responsivity of 0.96 A/W," *IEEE Photon. Technol. Lett.*, vol. 4, pp. 1241–1241, 1992.

- [42] G.-K. Chang, D. Guidotti, F. Liu, Y.-J. Chang, Z. Huang, V. Sundaram, D. Balaraman, S. Hegde, and R. Tummala, *Optoelectronic Integration* for a Tbps Mixed Signal System Module.

- [43] T. Suzuki, T. Nonaka, S.-Y. Cho, and N. M. Jokerst, "Embedded optical interconnections on printed wiring boards," in *Proc. 53rd ECTC Conference*, New Orleans, LA, May 2003, pp. 1153–1153.

- [44] S.-Y. Cho, J. D. Hall, A. Chellappa, N. M. Jokerst, and M. Brooke, "High speed optical interconnections using embedded PD's on electrical boards," in *Proc. 53rd ECTC Conference*, New Orleans, LA, May 2003, pp. 1046–1046.

- [45] S.-Y. Cho and M. A. Brooke, "Optical interconnections on electrical boards using embedded active optoelectronic components," *IEEE J. Select. Topics Quantum Electron.*, vol. 9, pp. 465–465, 2003.

- [46] S.-Y. Cho and N.-M. Jokerst, "Polymer waveguide optical interconnections for electrical interconnection substrates," in *Proc. IEEE Conf. on Lasers and Electro-Optics*, vol. 1, 2002, pp. 161–161.

- [47] D. C. Keezer, D. Minier, and M. C. Caron, "A production-oriented multiplexing system for testing above 2. 5 Gbps," in *Proc. IEEE Int. Test Conf. (ITC'03)*, Charlotte, NC, Oct., pp. 191–200.

- [48] J. S. Davis, D. C. Keezer, O. Liboiron-Ladouceur, and K. Bergman, "Application and demonstration of a digital test core: Opto-electronic test bed and wafer-level prober," in *Proc. IEEE Int. Test Conf. (ITC'03)*, Charlotte, Oct. 2003, pp. 166–174.

- [49] D. C. Keezer, J. S. Davis, S. Bezos, D. Minier, and M. C. Caron, "Low-cost strategies for testing Multi-GigaHertz SOP's and components," in *Proc. IEEE Electronics Packaging Technology Conf.* (*EPTC'03*), Singapore, Dec. 2003, pp. 410–444.

- [50] S. Bhattacharya, G. Srinivasan, and A. Chatterjee, "Testing of wireless data transceivers using periodic bitstreams," in *Proc. VLSI Test Sympo*sium, 2004.

- [51] S. Cherubal et al., "Concurrent testing of RF power amplifiers," in Proc. VLSI Design Conference, Jan. 2004, pp. 100–106.

- [52] R. C. Dunne and S. K. Sitaraman, "An integrated process modeling methodology and module for sequential multilayered substrate fabrication using a coupled cure-thermal-stress analysis approach," *IEEE Trans. Electron. Packag. Manufact.*, vol. 25, pp. 326–334, Dec. 2002.

- [53] R. C. Dunne, S. K. Sitaraman, S. Luo, C. P. Wong, W. E. Estes, and M. Periyasamy, "Cure kinetics modeling and process optimization of the ViaLux 81 epoxy photo-dielectric dry film (PDDF) material for microvia applications," *J. Appl. Polymer Sci.*, vol. 84, pp. 691–700, 2002.

- [54] K. Tunga, J. Pyland, R. V. Pucha, and S. K. Sitaraman, "Study on the choice of constitutive and fatigue models in solder joint life prediction," in *Proc. ASME International Mechanical Engineering Congress and Exposition*, IMECE2002/EPP-39 676.

- [55] R. V. Pucha, J. Pyland, and S. K. Sitaraman, "Damage metric-based mapping approaches for developing accelerated thermal cycling guidelines for electronic packages," *Int. J. Damage Mechanics*, vol. 10, no. 3, pp. 214–234, 2001.

- [56] S. Michaelides and S. K. Sitaraman, "Die cracking and reliable die design for flip-chip assemblies," *IEEE Trans. Adv. Packag.*, vol. 22, pp. 602–613, Nov. 1999.

- [57] W. Xie, H. Hu, and S. K. Sitaraman, "Role of base substrate material on dielectric and copper interlayer separation," *Proc. The IMAPS International Journal of Microcircuits and Electronic Packaging*, vol. 25, no. 1, 2002.

- [58] M. Modi and S. K. Sitaraman, "Interfacial fracture toughness measurement for thin film interfaces," Eng. Fracture Mechan., to be published.

- [59] S. Hegde, R. V. Pucha, and S. K. Sitaraman, "Alternate dielectric and base substrate materials for enhanced reliability of high density wiring (HDW) substrates," J. Mater. Sci.: Mater. Electron., to be published.

- [60] R. V. Pucha, G. Ramakrishna, S. Mahalingam, and S. K. Sitaraman, "Modeling plastic strain gradient effects in low-cycle fatigue of copper micro-structures," Int. J. Fatigue, to be published.

- [61] S. Hegde, R. V. Pucha, D. Guidotti, F. Liu, R. Tummala, and S. K. Sitaraman, "Design, fabrication, and reliability testing of embedded optical interconnects on board," in *Proc. 54th Electronic Components and Technology Conference*, June 2004.

- [62] K. Lim, M. F. Davis, M. Maeng, S.-W. Yoon, S. Pinel, L. Wan, D. Guidotti, D. Ravi, J. Laskar, E. Tentzeris, V. Sundaram, G. White, M. Swaminathan, M. Brook, N. Jokerst, and R. Tummala, "Delvelopement of intellinget network communicator for the mixed signal communications using the system-on-a-packaging technology," in *Proc. 2003 Asia-Pacific Microwave Conference Digest*, 2003, pp. 1003–1006.

- [63] M. Maeng, K. Lim, Y. Hur, M. Davis, N. Lal, S.-W. Yoon, and J. Laskar, "Novel combiner for hybrid digital/RF fiber-optic application," in *Proc.* 2002 IEEE Radio and Wireless Conference, 2002, pp. 193–196.

**Rao R. Tummala** (M'81–SM'84–F'92) received the B.E. degree in metallurgical engineering from the Indian Institute of Science, Bangalore, and the Ph.D. degree in materials science and engineering (MSE) from the University of Illinois, in 1969.

He is an Endowed Chair Professor in electrical and computer engineering and MSE with the Georgia Institute of Technology (Georgia Tech), Atlanta. He is also the Founding Director of the Microsystems Packaging Research Center (PRC). The PRC is currently the largest and most comprehensive

microsystems packaging center involving 250 students, 30 faculty, and 50 global companies, and was funded by the National Science Foundation (NSF) as one of its Engineering Research Centers in the United States, the Georgia Research Alliance, and the electronics industry, where he is pioneering the system-on-a-package (SOP) vision for mixed-signal systems of the next decade. He is also a Temasek Professor, NUS, Singapore. Prior to joining Georgia Tech, he was an IBM Fellow where he invented a number of major technologies for IBM's products for packaging, displaying, printing, and magnetic storage that include LTCC and scale-up of multilayer alumina ceramic. He was also part of the pioneering team that developed the industry's first flat panel display based on gas discharge display. He was the Director of the Advanced Packaging Technology Laboratory for all of IBM in 14 labs across the United States, Europe, and Japan. He edited the first undergraduate textbook Fundamentals of Microsystems Packaging (New York: McGraw-Hill, 2001) currently used by 43 universities around the world. He edited the first modern book in packaging Microelectronic Packaging Handbook (1988) which began to catalyze the academic research and educational programs. During this time, he began to lecture and advise universities in this area throughout the United States. Three notable examples are: Chairman of Advisory Board at the Massachusetts Institute of Technology, Cambridge, from 1988 to 1993, at the University of California at Berkeley from 1984 to 1987, and at the University of Illinois, Urbana, from 1983 to 1986. He left IBM in October 1993 and, two weeks later, he wrote the winning NSF proposal for an NSF-Engineering Research Center on SOP. He has published 350 papers and holds 71 U.S. patents.

Dr. Tummala received 16 technical, outstanding, and corporate awards from IBM, the highest Faculty Award at Georgia Tech, alumni awards from the University of Illinois and IISc, the David Sarnoff award from the IEEE for MCM, the Dan Hughes Award from IMAPS, the Engineering Materials Award from ASME, the Total Quality Manufacturing Award from SME, and the IEEE's Major Educational Innovation award. He is a member of NAE, IMAPS, and the American Ceramic Society, and Past President of the IEEE CPMT and IMAPS societies.

Madhavan Swaminathan (A'01–M'95–SM'98) received the M.S. and Ph.D. degrees in electrical engineering from Syracuse University, Syracuse, NY.

He is currently a Professor with the School of Electrical and Computer Engineering, Georgia Institute of Technology (Georgia Tech), Atlanta, and the Deputy Director of the Packaging Research Center (PRC), Georgia Tech. He is the cofounder of Jacket Micro Devices, a company specializing in integrated passive devices for RF applications where he serves as the Chief Scientist. Prior to

joining Georgia Tech, he was with the Advanced Packaging Laboratory, IBM, working on packaging for super computers. While at IBM, he reached the second invention plateau. He has more than 150 publications in refereed journals and conferences, has coauthored three book chapters, has nine issued patents, and has nine patents pending. His research interests are in digital, RF, optoelectronics, and mixed-signal packaging with emphasis on design, modeling, characterization, and test.

Dr. Swaminathan is the recipient of the 2002 Outstanding Graduate Research Advisor Award from the School of Electrical and Computer Engineering, Georgia Tech and the 2003 Outstanding Faculty Leadership Award for the advisement of GRAs from Georgia Tech. He is also the recipient of the 2003 Presidential Special Recognition Award from IEEE CPMT Society for his leadership of TC-12. He has also served as the coauthor for a number of outstanding student paper awards at EPEP'00, EPEP'02, EPEP'03, ECTC'98, and the 1997 IMAPS Education Award and is the recipient of the Shri. Mukhopadyay best paper award at the International Conference on Electromagnetic Interference and Compatibility in 2003. He served as the Co-Chair for the 1998 and 1999 IEEE Topical Meeting on Electrical Performance of Electronic Packaging (EPEP), the Technical and General Chair for the IMAPS Next Generation IC & Package Design Workshop, and the Co-Chair for the 2001 IEEE Future Directions in IC and Package Design Workshop. He serves as the Chair of TC-12, the Technical Committee on Electrical Design, Modeling and Simulation within the IEEE CPMT society. He is the cofounder of the IMAPS Next Generation IC & Package Design Workshop and the IEEE Future Directions in IC and Package Design Workshop. He also serves on the Technical Program Committees of EPEP, Signal Propagation on Interconnects Workshop, Solid State Devices and Materials Conference (SSDM), Electronic Components and Technology Conference (ECTC), and Interpack. He has been a Guest Editor for the IEEE TRANSACTIONS ON ADVANCED PACKAGING and the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES. He was the Associate Editor of the IEEE TRANSACTIONS ON COMPONENTS AND PACKAGING TECHNOLOGIES.

**Manos M. Tentzeris** (SM'02) received the Diploma Degree in electrical and computer engineering from the National Technical University of Athens in Greece and the M.S. and Ph.D. degrees in electrical engineering and computer science from the University of Michigan, Ann Arbor, MI.

He is currently an Associate Professor with School of ECE, Georgia Institute of Technology (Georgia Tech), Atlanta, GA. He has helped develop academic programs in Highly Integrated Packaging for RF and Wireless Applications, Microwave

MEMs, SOP-integrated antennas and Adaptive Numerical Electromagnetics (FDTD, MultiResolution Algorithms) and heads the ATHENA research group. He is the Georgia Tech NSF-Packaging Research Center Associate Director for RF Research and the RF Alliance Leader. He is also the leader of the Novel Integration Techniques Subthrust of the Broadband Hardware Access Thrust of the Georgia Electronic Design Center (GEDC) of the State of Georgia. He was a Visiting Professor with the Technical University of Munich, Germany, during the summer of 2002. He has published more than 140 papers in refereed journals and conference proceedings and eight book chapters.

Dr. Tentzeris was the recipient of the 2003 and 2004 IBC International Educator of the Year Awards, the 2003 IEEE CPMT Outstanding Young Engineer Award, the 2002 International Conference on Microwave and Millimeter-Wave Technology Best Paper Award (Beijing, China), the 2002 Georgia Tech-ECE Outstanding Junior Faculty Award, the 2001 ACES Conference Best Paper Award, the 2000 NSF CAREER Award and the 1997 Best Paper Award, International Hybrid Microelectronics and Packaging Society. He was also the 1999 Technical Program Co-Chair of the 54th ARFTG Conference, Atlanta, GA and he is the Vice-Chair of the RF Technical Committee (TC16) of the IEEE CPMT Society. He is a member of URSI-Commission D, an Associate Member of EuMA and a member of the Technical Chamber of Greece.

Joy Laskar (S'84–M'85–SM'02) received the B.S. degree in computer engineering with math/physics minors (highest honors) from Clemson University, Clemson, SC, in 1985. He received the M.S. and the Ph.D. degrees in electrical engineering from the University of Illinois at Urbana-Champaign, Urbana, IL, in 1989 and 1991, respectively.

Prior to joining Georgia Tech in 1995, he has held faculty positions at the University of Illinois and the University of Hawaii. At the Georgia Institute of Technology (Georgia Tech), he holds the Joseph

M. Pettit Professorship of Electronics, is currently the chair for the Electronic Design and Applications Technical Interest Group, the Director of Georgia's Electronic Design Center, and the System Research Leader for the NSF Packaging Research Center. His research has focused on high frequency IC design and their integration. At Georgia Tech, he heads a research group with a focus on integration of high frequency electronics with optoelectronics and integration of mixed technologies for next generation wireless and optoelectronic systems. He has authored or co-authored more than 200 papers, several book chapters (including three textbooks in development), numerous invited talks, and has more than 20 patents pending. He is the faculty advisor for the 2000 IEEE MTT IMS Best Student Paper award. His research has produced numerous patents and transfers of technology to industry. Most recently his work has resulted in the formation of two companies. In 1998, he co-founded an advanced WLAN IC Company, RF Solutions, which is now part of Anadgics. In 2001, he co-founded a next generation interconnect company, Quellan, which is developing collaborative signal processing solutions for enterprise applications.

Dr. Laskar is a 1995 recipient of the Army Research Office's Young Investigator Award, a 1996 recipient of the National Science Foundation's CAREER Award, the 1997 NSF Packaging Research Center Faculty of the Year, the 1998 NSF Packaging Research Center Educator of the Year, the 1999 co-recipient of the IEEE Rappaport Award (Best IEEE Electron Devices Society Journal Paper), 2001 Georgia Tech Faculty Graduate Student Mentor of the year, recipient of a 2002 IBM Faculty Award, the 2003 Clemson University College of Engineering Outstanding Young Alumni Award, and the 2003 recipient of the Outstanding Young Engineer of the Microwave Theory and Techniques Society. For the 2004-2006 term, Professor Laskar has been appointed an IEEE Distinguished Microwave Lecturer for his seminar entitled "Recent Advances in High Performance Communication Modules and Circuits."

**Gee-Kung Chang** (M'82–SM'92) received the Bachelor degree in physics from National Tsinghua University in Taiwan in 1969 and the doctoral degree in physics from the University of California, Riverside, in 1976.

He spent the following two years carrying out postdoctoral research in high energy electron/photon physics at Rutgers University, NJ, and Cornell University, Ithaca, NY. He spent the next 23 years within the Bell Systems in New Jersey—Bell Labs, Bellcore, and Telcordia Technologies, where he

served in various capacities including Director of the Optical Networking Systems and Testbed, Director of the Optical System Integration and Network Interoperability, and finally, Executive Director and Chief Scientist of the Optical Internet Research Group. Prior to joining Georgia Tech, he served as Vice President and Chief Technology Strategist of OpNext, Inc., in charge of technology planning and product strategy for advanced optical networking devices and components. Currently, he is Byers Eminent Scholar Chair Professor and Georgia Research Alliance Eminent Scholar in Optical Networking in the School of Electrical and Computer Engineering at the Georgia Institute of Technology (Georgia Tech), Atlanta. He was the principal investigator of Internet Protocol (IP) directly over WDM systems using Optical-Label Switching techniques for the DARPA-sponsored Next-Generation Internet project. He was also in charge of WDM optical networking element design, system testing, integration, and interoperability of multivendors optical network rings for the MONET Washington, DC, Network field trials. The MONET Washington, DC network testbed was successfully completed in November 1999. He led a team to deliver a wide variety of software controlled and managed WDM optical

networking crossconnects in local exchange carrier (LEC) network testbed and provided high bandwidth real-time services and applications for the MONET New Jersey Area Network that demonstrated a national-scale reconfigurable transport WDM network. The MONET testbed result was demonstrated at OFC'97 in Dallas, TX. He led a team that designed and demonstrated the first reconfigurable, multiwavelength all-optical network testbed for the Optical Networks Technology Consortium in 1994. The ONTC testbed was delivered for world-first live wavelength reconfiguration demonstration of WDM rings using five Optical Add/Drop Multiplexers at OFC'95 in San Diego, CA, and subsequently to Northern Virginia for Bellcore's Customer Solution Forum in 1995. He has been granted 35 patents in the area of optoelectronic devices, high-speed integrated circuits, telecommunication switching components and systems, WDM optical networks ecurity, and optical label switching routers. He has coauthored over 140 journal and conference papers.

**Daniel Guidotti** received the M.A. and Ph.D. degrees in physics from the University of Chicago, IL, and the B.A. degree from the University of California at Berkeley.

He is a Senior Research Scientist in the Department of Electrical and Computer Engineering at the Georgia Institute of Technology (Georgia Tech), Atlanta. His research focus is in optodigital system design and integration. He has published 40 archival articles in physics, chemistry, and engineering, has six issued patents and ten pending patents. Before

joining Georgia Tech in 2002, He was with the IBM T. J. Watson Research Center, Yorktown Heights, NY, where he contributed to the development of numerous technologies and is the recipient of the IBM "Outstanding Technical Achievement Award," and the industry Best R&D 100 award. Prior to joining IBM, he made numerous discoveries as a Postdoctoral Fellow: Forbidden Optical Second Harmonic Generation from centro-symmetric semiconductors, Coherent Anti-Stokes–Raman Scattering from electronically excited states in Benzene, Raman Scattering from strain confined electron-hole liquid in Silicon, and electronically driven 1-D structural phase transitions in organic semiconductor polymers. His thesis dealt with surface plasma waves in liquid metals.

**Suresh K. Sitaraman** received the B.Eng degree from the University of Madras, the M.A.Sc in mechanical engineering from the University of Ottawa, Canada, and the Ph.D. degree in mechanical engineering from the Ohio State University, Columbus, OH.

He is with the School of Mechanical Engineering at the Georgia Institute of Technology (Georgia Tech), Atlanta. Prior to joining Georgia Tech in 1995, he was a Senior Scientist at IBM Corporation. His expertise is in the area of thermo-mechanical

modeling, reliability, and design of electronic packages. He guides a group of postdoctoral, doctoral, master's, and undergraduate students and has published extensively in journals and conferences. He leads the Reliability Thrust at the Packaging Research Center, Georgia Tech, and directs the Computer-Aided Simulation of Packaging Reliability (CASPaR) Lab.

Dr. Sitaraman received the Metro-Atlanta Engineer of the Year in Education Award in 1999, Outstanding Faculty Education Award from the Packaging Research Center in 1998, and the NSF-CAREER Award (formerly President's Young Investigator Award) in 1997. Dr. Sitaraman serves as an Associate Editor for IEEE TRANSACTIONS ON ADVANCED PACKAGING. Dr. Sitaraman is a Fellow of the American Society of Mechanical Engineers (ASME).

Her current research focus is high-speed optical interconnect integration on low-cost FR4 board.

**Kyutae Lim** received the B.S., M.S., and Ph.D. degrees from the Hanyang University, Seoul, Korea, in 1991, 1993, and 1996, respectively.

From 1996 to 2000, he has been with the Samsung Advance Institute of Technology, Kiheung, Korea, as a Member of Technical Staff, where he was involved in developing millimeter-wave wireless communication systems. From 1998 to 1999, he was with the Communication Research Lab, Tokyo, Japan, as a Research Fellow, where he had been developing 60 GHz antennas and packages. Since

January 2000, he has been with the Microwave Application Group at the Georgia Institute of Technology (Georgia Tech), Atlanta, as part of the research faculty. He has authored and coauthored over 70 journal and proceeding papers, holds two U.S. patents and is the author of one book chapter. His research interests include the analysis of the electromagnetic phenomenon, the passive and active circuit design for RF and optoelectronic applications and the mixed signal system integration by the system-on-packaging technology.

**David Keezer** (M'90–SM'03) received the Ph.D. degree from Carnegie-Mellon University, Pittsburgh, PA, the M.S. degree from the California Institue of Technology (Caltech), Pasadena, and the B.S. degree from the University of California at Berkeley. He also received the M.B.A. degree from the Florida Institute of Technology, Melbourne.

He is an Associate Professor of Electrical and Computer Engineering at the Georgia Institute of Technology (Georgia Tech), Atlanta. His research focuses on the design and test of high-performance

electronic systems. He has published over 120 articles on electronics testing. Prior to joining Georgia Tech in 1995, he was an Associate Professor at the University of South Florida, Tampa. He has worked for Harris Corporation, Intel Corporation, and IBM Corporation.

Lixi Wan received the B.S. degree in electrical engineering from the Xidian University, China, the M.S. degree in applied physics from Southwestern Jiaotong University, China, and the Ph.D. degree in electrical engineering from Beijing University of Posts and Telecommunication, China.

He was a Postdoctoral Researcher in Tsinghua University, Beijing, China, for two years. He was an Associate Professor of the Beijing University of Posts and Telecommunication from 1993 to 1998, and Research Fellow of the City University of Hong

Kong from 1997 and 1998. He joined the Electromagnetic Center, University of Illinois at Urbana-Champaign, as a Visiting Associate Professor from 1998 to 2000. He is a Research Engineer of the Packaging Research Center, Georgia Institute of Technology (Georgia Tech), Atlanta. He is author and coauthor of over 80 papers. His interest areas are fast algorithm of computation electromagnetic, design, modeling and simulation of mixed signal system, microwave, and antenna technologies.

Swapan K. Bhattacharya received the M.S. and Ph.D. degrees from the Indian Institute of Technology, Kharagpur, India.

He is a Senior Research Scientist at the Packaging Research Center (PRC), School of Electrical and Computer Engineering, Georgia Institute of Technology (Georgia Tech), Atlanta. During the past seven years, he has been working with high-performance electronics packaging at Georgia Tech.

**Fuhan Liu** received the M.S. degree in electron physics from Fudan University, Shanghai, China, in 1965.

Currently, he is a Research Engineer at NSF-Packaging Research Center (PRC) at the Georgia Institute of Technology (Georgia Tech), Atlanta. Prior to coming to the United States in 1997, he was an Associate Professor in the Department of Material Science and Deputy Director of High Density Electronic Packaging Laboratory at Fudan University. He had been a Visiting Scholar at

Brandeis University (1987–1988), Wayne State University (1997–1998), and International Microelectronics and Packaging Society (IMAPS, 1997). Currently, he focuses on the R&D of fabrication and integration of high-density wiring and optoelectronics for systems-on-package, material evaluation, processes development, and testing.

Dr. Liu received the Global Collaboration Award for his outstanding contributions to the NSF Programs and numerous national outstanding awards from China. His paper on "Nitrogen Temperature Super-Conducting Ring Experiment" was voted as the "Memorable Paper of the *American Journal of Physics* (AJP) since 1933" and his name was listed in the "AJP All-Star" team.

**Venky Sundaram** received the B.S. degree in metallurgical engineering from the Indian Institute of Technology, Bombay, and the M.S. degree in ceramic and materials engineering from the Georgia Institute of Technology (Georgia Tech), Atlanta.

He is a research staff member with Georgia Tech Packaging Research Center (PRC) and is currently coleading the SOP package substrate development program at the PRC. He is also a Ph.D. degree candidate in materials science and engineering at Georgia Tech. He has more than seven years

experience in high-density microvia board and thin-film technology. He has more than 30 publications, four patents pending, and a number of invention disclosures in SOP substrate technology and RF/digital packaging. He has presented industry short courses on "Embedded Passives" and "High Density PWB Technologies."

Mr. Sundaram is a member of the High Density Substrate Technical Committee (TC-6) of the IEEE-CPMT society, PRC program manager for the SOP Technology Transfer Partnership with Endicott Interconnect, New York, and the High-Density Substrate Task Leader for the multimillion dollar Nano-Wafer Level Packaging Program.

**P. Markondeya Raj** received the Ph.D. degree in ceramic engineering from Rutgers University, NJ.

He is currently a Research Engineer at the Packaging Research Center (PRC), Georgia Institute of Technology (Georgia Tech), Atlanta. His research interests include embedded components for passives using chemical solution methods, nanowafer-level packaging and new substrate materials based on low-cost ceramic matrix composites. He has over 55 publications and coauthored two books.