## **ENGR-2300**

# **Electronic Instrumentation**

Quiz 3

Fall 2019

| Name SOLUTIONS                            |  |  |  |  |

|-------------------------------------------|--|--|--|--|

| Section                                   |  |  |  |  |

|                                           |  |  |  |  |

| Question 1 (20 Points)                    |  |  |  |  |

| Question 2 (20 Points)                    |  |  |  |  |

| Question 3 (20 Points)                    |  |  |  |  |

| Question 4 (20 Points)                    |  |  |  |  |

| LMS Question is worth an additional 20pts |  |  |  |  |

| Total (80 points)                         |  |  |  |  |

On all questions: **SHOW ALL WORK**. BEGIN WITH FORMULAS, THEN SUBSTITUTE VALUES <u>AND UNITS</u>. No credit will be given for answers that appear without justification. Read the entire quiz before answering any questions. Also it may be easier to answer parts of questions out of order.

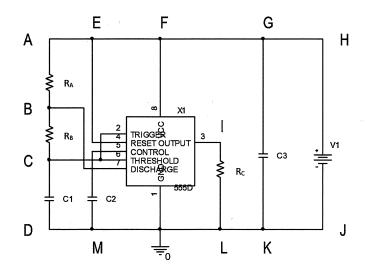

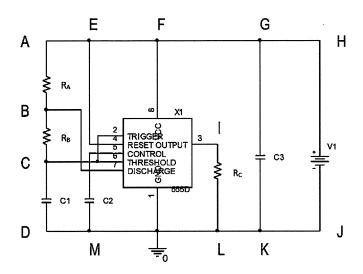

## Question 1 (20 Points) Astable Multivibrator (An Iconic 555 Timer Application)

a. A 555 timer, a stable multivibrator is built as above with  $R_A = 10 k\Omega$ ,  $R_B = 9.1 k\Omega$ ,  $R_C = 40 k\Omega$ ,  $C1 = 0.1 \mu F$ ,  $C2 = 0.01 \mu F$ ,  $C3 = 330 \mu F$ , and V1 = 9V. Determine the **on time** (T1) and the **off time** (T2) for this circuit. (4 Pts)

$$T_1 = 0.693 (R_A + R_B) C_1 = 1.324 \text{ m s}$$

$$T_2 = 0.693 (R_B) C_1 = 0.631 \text{ m s}$$

$$D = \frac{T_1}{T_1 + T_2} \times 100 \text{ /.} = 67.73 \text{ /.} \qquad T_1 + T_2 = 1.95 \text{ ms}$$

$$\approx 2 \text{ ms}$$

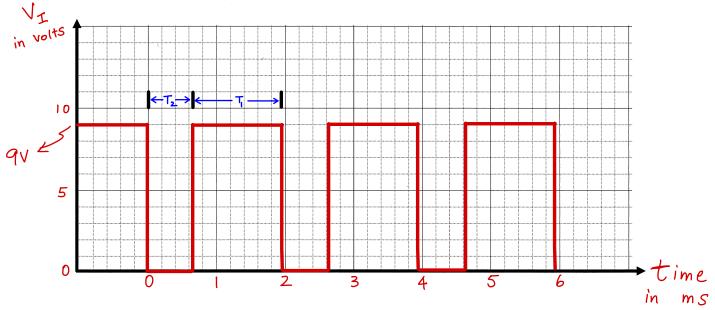

**b.** Plot the output voltage (I) below, showing at least two full cycles, starting with the output voltage at its maximum (assume = 9V). Label the horizontal and vertical scales. (4 Pts)

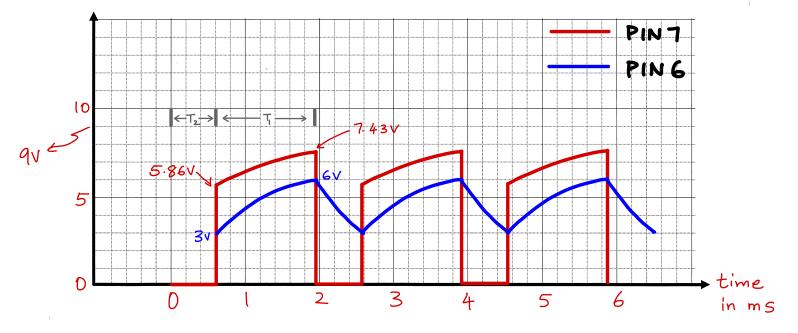

**c.** Determine the maximum and minimum voltages at pins 6 (C) and 7 (B). Assume that the circuit is in steady state. You may want to look at the background information provided in the crib sheet.(4 Pts)

$$V_{6,min} = \frac{1}{3} V_{cc} = \frac{q}{3} = 3V \qquad V_{6,max} = \frac{2}{3} V_{cc} = \frac{18}{3} = 6V$$

$$V_{7,min} = 0V \qquad V_{7,max} = V_{6,max} + V_{RB} \qquad V_{RB} = (V_{CC} - V_{6,max}) \cdot \frac{R_B}{R_A + R_B}$$

$$= 6 + 1.43 = 7.43 V$$

**d.** Plot at least two cycles of the voltage at pins 6 & 7. Label the vertical and horizontal scales.

(4 Pts)

$$V_{7,\text{switch}} = V_{6,\text{min}} + V_{RB}$$

= 3 + 2 \*86 = 5 \*86 V  $V_{RB} = (V_{CC} - V_{6,\text{min}}) \cdot \frac{R_B}{R_A + R_B}$

This is the same figure as part a.

e. Modify the circuit to achieve a 90% duty cycle. You are only allowed to change only one resistor and no other components. The frequency is allowed to change. Which resistor do you change and what is the new value? (4 Pts)

Values for Part a. were:  $R_A=10k\Omega$ ,  $R_B=9.1k\Omega$ ,  $R_C=40k\Omega$ ,  $C1=0.1\mu F$ ,  $C2=0.01\mu F$ ,  $C3=330\mu F$ , and V1=9V.

Duty cycle,

$$D = \frac{R_A + R_B}{R_A + 2 R_B} = 0.9$$

$$\Rightarrow$$

$R_A = 8R_B$

Change either RA or RB

Keep

$$R_B = 9.1 \text{K}_{52}$$

then  $R_A = 12.8 \text{K}_{52}$

Keep

$$R_A = 9.1 \text{Ks2}$$

then  $R_B = 1.25 \text{Ks2}$

#### **Question 2 (20 Points) Combinational & Sequential Logic Circuits**

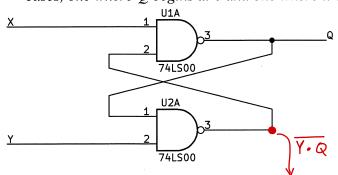

a. (4 points) Determine the truth table for the following circuit. Note that you have to do two cases, one where Q begins at 0 and one where it begins at 1.

| Q Before | X | Y | Work space | Q After  |

|----------|---|---|------------|----------|

| 0        | 0 | 0 |            | <u> </u> |

| 0        | 0 | 1 |            |          |

| 0        | 1 | 0 |            | 0        |

| 0        | 1 | 1 |            | 0        |

| 1        | 0 | 0 |            | 1        |

| 1        | 0 | 1 | 0          |          |

| 1        | 1 | 0 |            | 0        |

| 1        | 1 | 1 | 0          | l        |

| A   | B | Ä·B                          |

|-----|---|------------------------------|

| 0   | 0 | 1                            |

| 0   | 1 | I                            |

| l   | D | l                            |

| . U | l | 0                            |

| 14  |   | I<br>input is 'O',<br>ie 'I' |

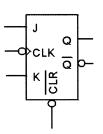

**b.** (4 points) The desired output of a negative edge triggered JK flip flop after the pulse is Q = 0 and Qbar = 1. How can this be achieved? List all possible input conditions for this to happen, i.e. what should be done with J, K, clock, and clear inputs. You are given that the outputs before pulse are Q = 1and Obar = 0.

- Toggle: J=1, K=1, Clear=1, Clock= V

- Kill/Reset: J=0, K=1, Clear=1, Clock=

- J=0/1, K=0/1, clear = 0, clock = V

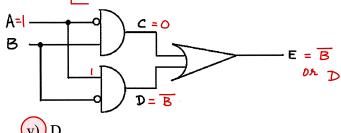

- - c. (2 points) Given A = Logic '1', E = ?

- Note: Bubble indicates inversion!

- Circle the correct answer.

- i) Logic '0'

- ii) Logic '1'

- iii) C

- iv) B

- Either

- vii) A.B

- viii) A + B

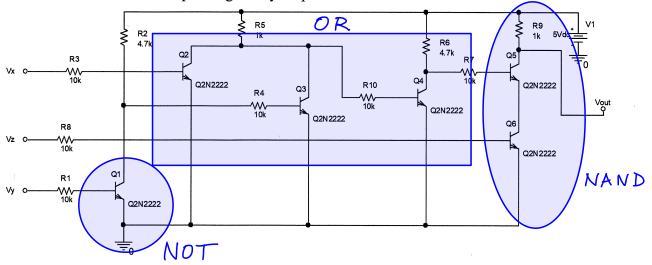

**d.** (10 points) The circuit below consists of a npn transistor network that implements a logic function between three input variables X, Y, and Z. The binary variables X, Y, and Z are represented using voltages Vx, Vy, and Vz respectively. Vout represents the output voltage of the network for corresponding binary output variable OUT.

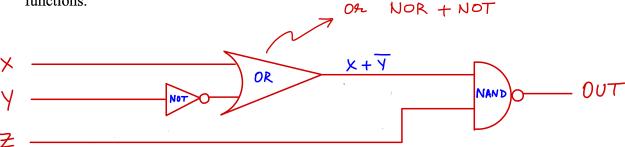

i) (6 points) Draw the logic diagram for the above circuit. Use logic gate symbols and show how the inputs X, Y, Z are related to output OUT. For this you need to identify how transistors, and serial/parallel connections of transistors, can be used to implement logic functions.

ii) (4 points) Fill the truth table below based on the logic diagram derived in previous part, or directly from the given transistor network.

| X   | Y | Z | OUT |

|-----|---|---|-----|

| 0   | 0 | 0 | 1   |

| 0   | 0 | 1 | 0   |

| . 0 | 1 | 0 |     |

| 0   | 1 | 1 | l   |

| 1   | 0 | 0 | ١   |

| 1   | 0 | 1 | 0   |

| 1   | 1 | 0 | l   |

| 1   | 1 | 1 | 0   |

$$OuT = \overline{(X+\overline{Y})} \cdot \overline{Z}$$

$$= \overline{X+\overline{Y}} + \overline{Z}$$

$$= \overline{X} \cdot \overline{Y} + \overline{Z}$$

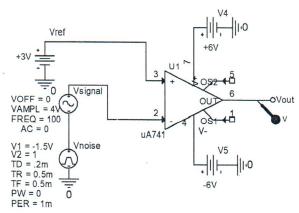

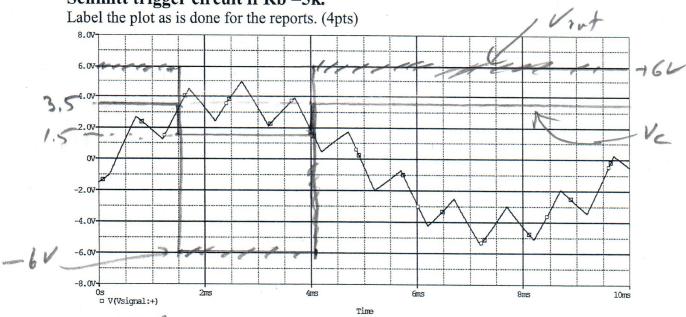

## Question 3 (20 Points) Schmitt Trigger

In this problem, we investigate the same properties of Schmitt Triggers we did in Experiment 6. Assume the output of the op-amps is capable of reaching the power supply voltages, +6V and -6V in this example.

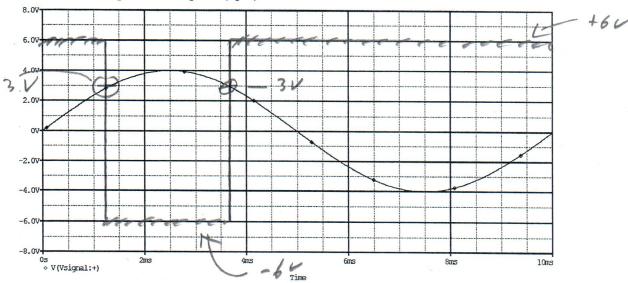

a. For the circuit shown the input signal, Vsignal is compared to Vref. For this part there isn't any noise. Vnoise amplitude is 0V. The plot below has the Vsignal (without noise).

On this plot, draw Vout. Label the plot as you would for an experiment report. (4pts)

50/n.

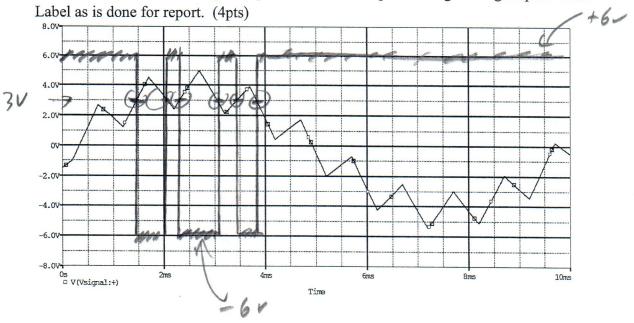

b. Same circuit but now a triangle shaped noise has corrupted the signal. Again plot Vout.

c. This is now the same circuit but configured as a Schmitt Trigger. Vc is the voltage at the non-inverting input of the op amp. Ra=1k $\Omega$ . The goal here is to determine values of Rb that will eliminate false output transitions caused by the noise signal.

Vref

1k

Vc

1k

Vc

1k

Vc

3

Voise

Voise

Voise

Voise

Vinoise

Vinoi

Rb

What is the maximum value of Vout? (1pt)  $\frac{\cancel{16} \cancel{V}}{\cancel{10}}$

What is the minimum value of Vout? (1pt) - 6V

Complete the table below, use the figure in part d to help fill in the final column: (6pts)

| obspress the their sole with the part a to neep jui in the juit column. (opts) |              |                    |                  |                  |              |

|--------------------------------------------------------------------------------|--------------|--------------------|------------------|------------------|--------------|

|                                                                                | $Rb(\Omega)$ | Vc if $Vout = max$ | Vc if Vout = min | Eliminates false |              |

|                                                                                |              |                    |                  | pulses (Y on N)  |              |

|                                                                                | 5k           | 3.50               | Vi= 3+ 5(-0-1)   | K                | Blot )       |

|                                                                                | 14k          | 3.24               | 2.40             | N                | bolone       |

| 31                                                                             | a Mo W       | -06v               | 30 W W W 6       | 06v              | 3+1/-9)=2.40 |

| ¥:                                                                             | 3+ (6-3) 6   | - 73.5V            | Ve= 3+ (6-3)     | 1 = 3.1V         |              |

d. Below is the same figure as shown in part b. Now plot Vout and Vc for the Schmitt trigger circuit if Rb =5k.

Note: Py = 144 transitions at 3.2V + 2.4 ~ nill

have extra pulses

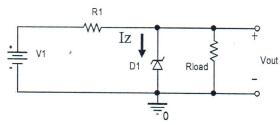

## Question 4 (20 Points) Diode Circuits

a. (6pts) In the circuit shown:

V1 = 15V

$R1=200\Omega$

Rload= $600\Omega$

D1 is a Zener. Two different Zener diodes are tried with this circuit. Determine Vout, Iz (the current in the Zener), IR1 (the current in R1) and the power loss in the Zener for each case. Use the "Some Additional Background" information provided in the crib sheets. (6pts)

| Zener part<br>number | Vout         | Iz   | $I_{R1}$ | Power loss in<br>Zener |

|----------------------|--------------|------|----------|------------------------|

| 1N749A               | 4.3V         | 32mA | 53.5mA   | 0.14 W                 |

| 1N759A<br>12 V       | 15/300)=1110 | 0    | 18,75mA  | 0                      |

4.3 V = 1  $V_{out} = 4.3 V$   $I_{out} = \frac{15-43}{200} = 53.5 A$   $I_{out} = \frac{4.3}{600} = 21.5 M$ 1 It 28 mer active  $f_{100d} = \frac{2}{600} = 20$   $I_{out} = \frac{1}{4}$   $I_{out} = \frac{4.3}{3} \times 32$   $I_{out} = \frac{4$

limiting. Refer to "Additional Background"

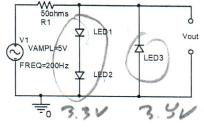

(3pts) Sketch and label Vout on the plot. V1 is already plotted.

LED1 is an Pure Green LED (555 nm) 2.1

LED2 is a Super Red LED (633 nm)

LED3 is an Ultra Blue LED (430 nm)

ii. (1pt)What is the peak current through LED1?

5/ent -3.3 V = 34 ml

iii. (1pt)What is the peak current through LED2?

5-3.8 = 24m/ OR -24mA

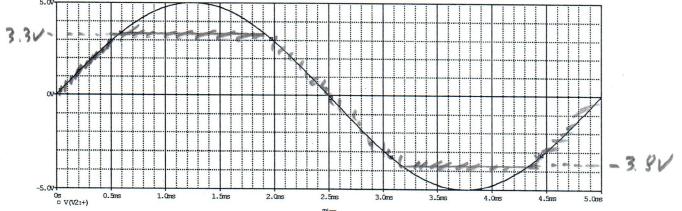

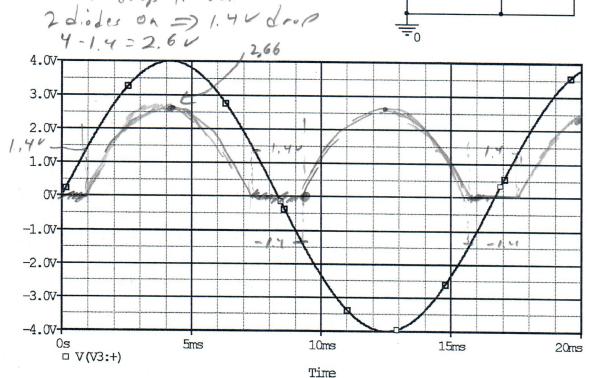

c. Rectifier diodes: The voltage across Rload is the output voltage. The plot shows the input voltage. Plot the output voltage using the Von diode model of a 4148 diode. Label important voltages including the peak output voltage. (3pts)

VAMPL = 4

FREQ = 60

V3

V3

D1

D2

Ik Rload

D3

D4

D<sub>1</sub> 50uFC1

1k

D<sub>3</sub>

Rload

D<sub>2</sub>

D4

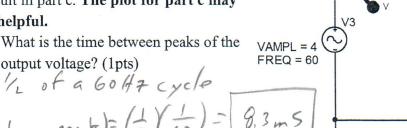

**d.** A filter capacitor has been added to the circuit in part c. The plot for part c may be helpful.

output voltage? (1pts) Peak in 1/2 of a 60H7 cycle

At the time of the peak output voltage, what is the current in Rload, (the load resistance)?

2.6 V/1/ = 2.6 mA Rload =  $1k\Omega$  (1pt)

iii. Immediately after when the voltage peak the diodes will turn off. All of the current in R1 at this time must be supplied by C1. If C1=50uF, what is the dV/dt for the capacitor at

this time? The Crib Sheet for Quiz 1 may be useful. (2pts)  $V_{c} = 2..6 \text{ V} \quad I_{R} = 2.6 \text{ mA} \qquad I = C \quad \text{TH} \qquad \frac{2.6 \text{ mA}}{5 \times 10^{3}} = 52 \text{ //sec}$ = 52mv/ms

iv. Do a crude estimate of the ripple voltage by assuming that the dV/dt (part iii) is constant for a time equal to the time between voltage peaks (part i). (1pts)

AV 2 LV. At = (52 × 8.3×103) = 0.43V 2 Vrigits

- e. Do you expect to take the optional final? Your answer here is NON-BINDING. (1pt) The optional final will:

- cover all topics in the class,

- generally be more difficult than the quizzes

- Not have an LMS portion,

- replace your lowest quiz grade, which includes the LMS portion,

NOT replace your lowest quiz grade, IF the final grade is the lowest. i.e. you cannot hurt you overall grade by attempting the final.

11