# Table of Contents

| SECTION 1          | 1.1 | Standard Version of ADPCM            | 1-1  |

|--------------------|-----|--------------------------------------|------|

| Introduction       | 1.2 | Non-Standard Version of ADPCM        | 1-2  |

| SECTION 2          | 2.1 | Trade-Offs                           | 2-1  |

| Speech Coding      | 2.2 | Advantages of Digital Speech Coding  | 2-2  |

| SECTION 3          | 3.1 | Uniform PCM                          | 3-2  |

| Types of           | 3.2 | Logarithmic PCM                      | 3-5  |

| Speech Coders      | 3.3 | ADPCM Coding                         | 3-7  |

| SECTION 4          | 4.1 | The Encoder Algorithm                | 4-4  |

| The CCITT<br>ADPCM | 4.2 | The CCITT Decoder Algorithm4-18      |      |

| Algorithm          |     |                                      |      |

| SECTION 5          | 5.1 | I/O Interface                        | 5-3  |

| ADPCM              | 5.2 | Standard Implementation              |      |

| Implementation     |     | 5.2.1 Code Structure                 | 5-6  |

| on the             |     | 5.2.2 Initialization                 | 5-9  |

| DSP56001           |     | 5.2.3 PCM Format Conversion          | 5-12 |

|                    |     | 5.2.4 Logarithmic Conversion         | 5-14 |

|                    |     | 5.2.5 Floating-Point Conversion      | 5-17 |

|                    |     | 5.2.6 Difference Signal Quantization | 5-19 |

|                    |     | 5.2.7 Inverse Quantization           | 5-22 |

|                    |     | 5.2.8 Adaptive Predictor             | 5-24 |

## Table of Contents

|     | 5.2.9 Tone Detection           | 5-31 |

|-----|--------------------------------|------|

|     | 5.2.10 Scale Factor Adaptation | 5-32 |

|     | 5.2.11 Decoder Synchronization | 5-34 |

| 5.3 | Non-Standard Implementation    | 5-34 |

|     | 5.3.1 Code Structure           | 5-36 |

|     | 5.3.2 Initialization           | 5-37 |

|     | 5.3.3 Format Conversions       | 5-40 |

|     | 5.3.4 Adaptive Predictor       | 5-41 |

| 5.4 | Optimization Techniques        | 5-43 |

| 5.5 | Performance Specifications     | 5-52 |

| Appendix A | Terminology | A-1         |

|------------|-------------|-------------|

| References |             | Reference-1 |

# Illustrations

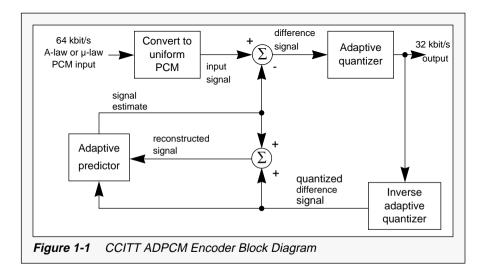

| Figure 1-1 | CCITT ADPCM Encoder Block Diagram                   | 1-2  |

|------------|-----------------------------------------------------|------|

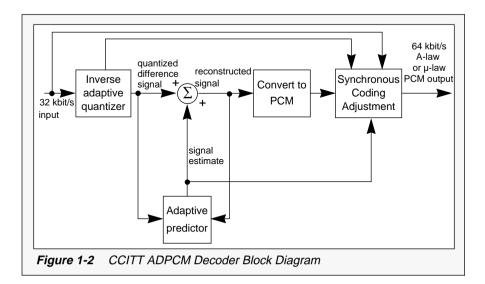

| Figure 1-2 | CCITT ADPCM Decoder Block Diagram                   | 1-3  |

|            |                                                     |      |

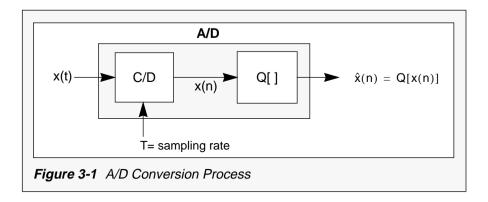

| Figure 3-1 | A/D Conversion Process                              | 3-2  |

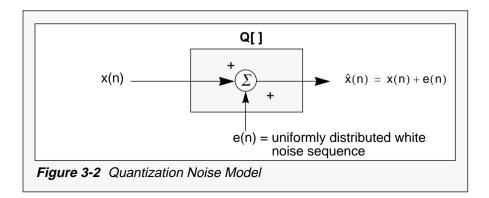

| Figure 3-2 | Quantization Noise Model                            | 3-3  |

| Figure 3-3 | Uniform Quantizer                                   | 3-4  |

| Figure 3-4 | Feedforward APCM Coder                              | 3-8  |

| Figure 3-5 | Feedback APCM Coder                                 | 3-8  |

| Figure 3-6 | DPCM Coder                                          | 3-9  |

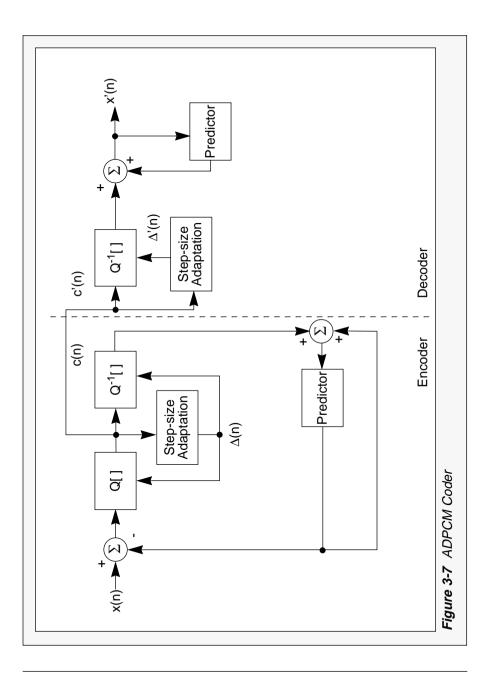

| Figure 3-7 | ADPCM Coder                                         | 3-11 |

|            |                                                     |      |

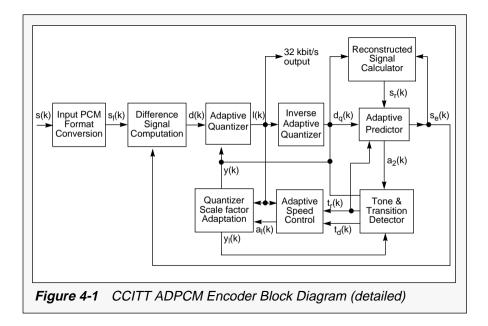

| Figure 4-1 | CCITT ADPCM Encoder Block Diagram (detailed)        | 4-3  |

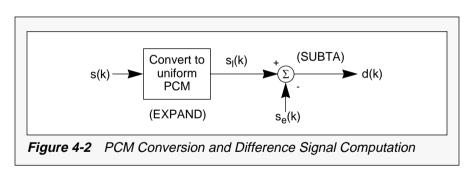

| Figure 4-2 | PCM Conversion and Difference Signal<br>Computation | 4-5  |

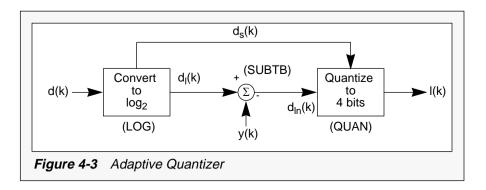

| Figure 4-3 | Adaptive Quantizer                                  | 4-6  |

| Figure 4-4 | Inverse Adaptive Quantize                           | 4-7  |

| Figure 4-5 | Adaptive Prediction Filter                          | 4-8  |

| Figure 4-6 | Predictor Pole Coefficient Adaptation for $a_1(k)$  | 4-10 |

| Figure 4-7 | Predictor Pole Coefficient Adaptation for $a_2(k)$  | 4-11 |

| Figure 4-8 | Predictor Zero Coefficient Adaptation               | 4-12 |

# Illustrations

| Figure 4-9  | Scale Factor Adaptation                               | 4-13 |

|-------------|-------------------------------------------------------|------|

| Figure 4-10 | Speed Control Parameter Adaptation                    | 4-15 |

| Figure 4-11 | Tone Detection                                        | 4-17 |

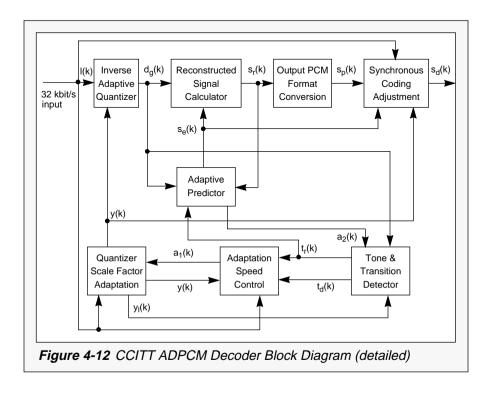

| Figure 4-12 | CCITT ADPCM Decoder Block Diagram (detailed)          | 4-19 |

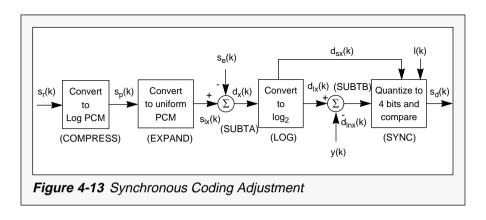

| Figure 4-13 | Synchronous Coding Adjustment                         | 4-20 |

|             |                                                       |      |

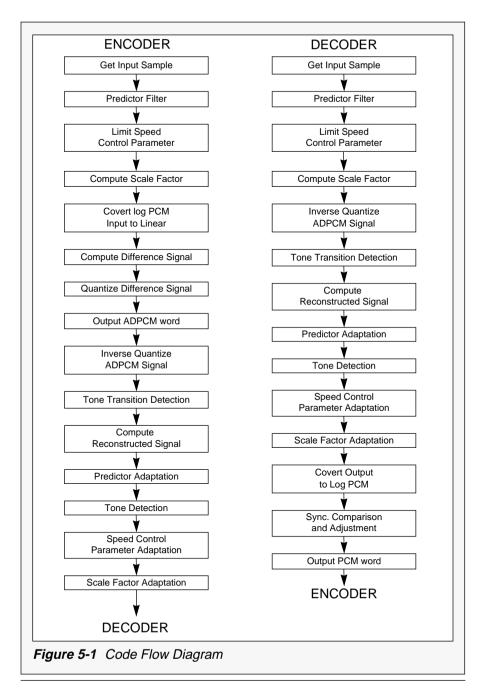

| Figure 5-1  | Code Flow Diagram                                     | 5-8  |

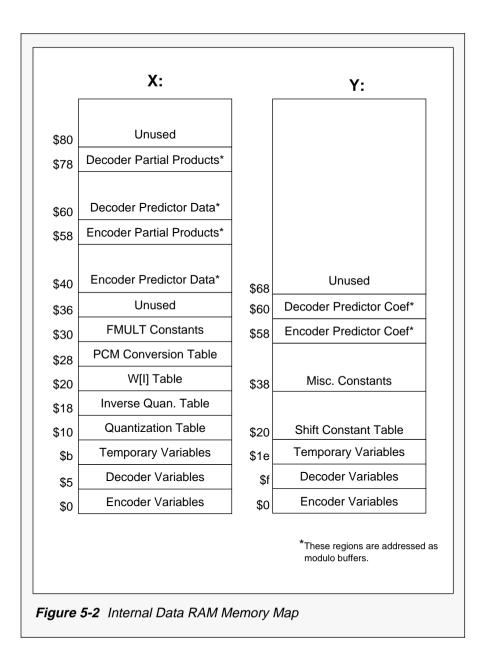

| Figure 5-2  | Internal Data RAM Memory Map                          | 5-11 |

| Figure 5-3  | Address Register Usage                                | 5-12 |

| Figure 5-4  | Linear to Log Conversion Routine                      | 5-16 |

| Figure 5-5  | Linear to Floating-Point Conversion Routine           | 5-18 |

| Figure 5-6  | Difference Signal Scaling and Quantization            | 5-20 |

| Figure 5-7  | Inverse Quantization and Scaling of<br>ADPCM Codeword | 5-23 |

| Figure 5-8  | Adaptive Predictor Data Structure                     | 5-27 |

| Figure 5-9  | Internal Data RAM Memory Map (Non-standard)           | 5-39 |

| Figure 5-10 | Address Register Usage (Non-standard)                 | 5-39 |

| Figure 5-11 | Adaptive Prediction Filter                            | 5-42 |

| Figure 5-12 | Adaptive Predictor Data Structure (Non-standard)      | 5-43 |

# List of Tables

| Table 4-1 | Quantizer Normalized Input/Output Characteristic | 4-6  |

|-----------|--------------------------------------------------|------|

| Table 4-2 | W(I) Lookup Table                                | 4-14 |

| Table 4-3 | F[I(k)] Lookup Table                             | 4-16 |

|           |                                                  |      |

| Table 5-1 | Memory Usage                                     | 5-53 |

| Table 5-2 | Code Execution Times                             | 5-55 |

#### **SECTION 1**

"This application report will first point out some of the advantages of speech coding in general and then some of the particular advantages of the CCITT standard."

## Introduction

This application report describes the implementation of an Adaptive Differential Pulse Code Modulation (ADPCM) speech coder on the Motorola DSP56001 digital signal processor. The algorithm described in this document has been standardized by the International Telegraph and Telephone Consultative Committee (CCITT) in Recommendation G.721 [1] for digital speech coding in a telecommunications environment. The standard, as defined by the CCITT, specifies the translation of µ-law or A-law PCM encoded speech at 64 kbit/s to ADPCM encoded speech at 32 kbits to provide a 2 to 1 compression of the speech signal with very little perceptual loss of speech quality. The algorithm also has added complexity to handle non-speech signals such as modem signals. The block diagrams of the CCITT ADPCM encoder and decoder are shown in Figure 1-1 and Figure 1-2.

### 1.1 Standard Version of ADPCM

Two implementations of the ADPCM algorithm on the DSP56001 are described in this document. The first implementation adheres completely with the CCITT Recommendation G.721 (revised version dated August 1986). It provides bit-for-bit compatibility with the

test vectors described in G.721, meaning that the code correctly passes all the digital test sequences defined by the CCITT. In addition to providing compatibility with the standard, this implementation provides full-duplex operation. This means that one DSP56001 is able to perform both an encode and a decode in real-time.

### 1.2 Non-Standard Version of ADPCM

The second implementation also provides full-duplex ADPCM operation on a single DSP56001. This non-standard version implements the same algorithm as the standard version but does so more efficiently. As a result, this version requires less computational power and uses less memory than the standard version. In addition, the code provides a more direct, readable implementation of the algorithm, which permits easier modification of the code.

This application report presents some of the advantages of speech coding, followed by some of the particular advantages of the CCITT standard. The basic concepts of ADPCM and a detailed description of the actual CCITT algorithm are also included. After a description of the algorithm, the implementation of the algorithm on the DSP56001 is discussed, including various techniques used to improve performance. Finally the real-time performance and other technical characteristics of the DSP56001 implementations are described. ■

#### **SECTION 2**

## Speech Coding

"Digital signals ... are less sensitive to transmission noise and they are easier to multiplex, error protect, and encrypt for security than analog signals." **S**peech coding, or speech compression, is one of the major application areas for digital signal processing in the field of speech processing. The goal of speech coding is to digitally code speech efficiently for either storage or transmission. In telecommunication applications, the goal is typically to code an analog speech signal into a digital format, transmit the digital signal, and then decode the digital signal back into an analog waveform — all in real time.

#### 2.1 Trade-Offs

While the goal seems very simple, there are many trade-offs to be considered in a practical application. These trade-offs include decoded speech quality, transmission bandwidth, coder complexity, overall system cost, and real-time considerations. Different applications may have very different requirements. For example, military communication applications often sacrifice coder complexity and speech quality to achieve very low transmission bandwidths. Other applications, such as some voice mail systems, may not require real-time performance.

## 2.2 Advantages of Digital Speed Coding

Digital speech coding has advantages beyond the compression savings. Digital signals in general have many desirable properties: they are less sensitive to transmission noise and they are easier to multiplex, error protect, and encrypt for security than analog signals. Since coding algorithms can be implemented in software, modifications and improvements to algorithms are much easier than with dedicated hardware. In many applications such as computer workstations, a common DSP may perform several functions. These applications can add speech coding to a system without adding additional

As noted above, the ADPCM algorithm defined by the CCITT is intended for use in a telecommunications environment, although it may be applied in other areas. The CCITT algorithm actually implements a PCM/ADPCM/PCM conversion process and is called a transcoder for this reason. The standard is intended for use on digital channels that contain the digital equivalent of analog signals on analog telephone channels, so the CCITT algorithm has added complexity to handle non-speech signals (such as modem and DTMF signals) that may be present on analog telephone channels. It provides 2 to 1 compression allowing two ADPCM coded signals to be easily multiplexed into one basic 64-kbit/s digital channel.

#### **SECTION 3**

## Types of Speech Coders

"... logarithmic PCM (log PCM) coding, effectively compresses the input signal at the transmission end and expands it at the receiving end." Although there are many different methods for speech coding, these methods generally fall into two main categories: waveform coders and source coders. Waveform coders deal with speech on a sample by sample basis. Their goal is to have the output waveform of the decoder match the original speech waveform as closely as possible. Source coders (also called vocoders), on the other hand, attempt to describe a speech signal in terms of parameters of a speech production model. These models typically estimate vocal tract shape and vocal tract excitation. Vocoders can operate at much lower bit rates than waveform coders but their output speech quality is generally not as good. ADPCM is classified as a waveform coder and is actually a combination of several basic waveform coding techniques. It should also be noted that many speech coding algorithms are hybrids that combine a variety of techniques. For instance, ADPCM techniques are used in portions of many other coder algorithms, such as subband codand I PC coders ers

As noted above, ADPCM is a combination of several basic techniques. The following discussion is a brief

introduction to these techniques. Reference [2] also provides a good introduction to the topics discussed here as well as other types of speech coders.

### 3.1 Uniform PCM

In any digital speech coding system, an analog speech signal must be converted into a digital representation before it can be processed. Most digital coders use a form of pulse-code modulation (PCM) for the A/D conversion. The A/D conversion process is represented by a combination of two processes:

- a continuous-to-discrete conversion (C/D)

- a quantization (Q[]), as shown in Figure 3-1 [3]

The C/D conversion changes a continuous time waveform into a discrete time waveform with continuous amplitude. Mathematically, this process will

not introduce any error into the input signal as long as the sampling rate is at least twice the highest frequency of the input signal. The quantizer maps each continuous amplitude sample into a digital codeword. The mapping process represented by the function (Q[]) is called the quantizer characteristic.

The quantization process will introduce an error called the quantizer error into the signal. This error can be represented as an additive white noise source in the quantizer as shown in Figure 3-2. In speech applications, this error will be evident as audible noise at the D/A output. In many speech coding applications, this quantization noise is expressed in terms of Signal-to-Quantization Noise Ratio (SNR).

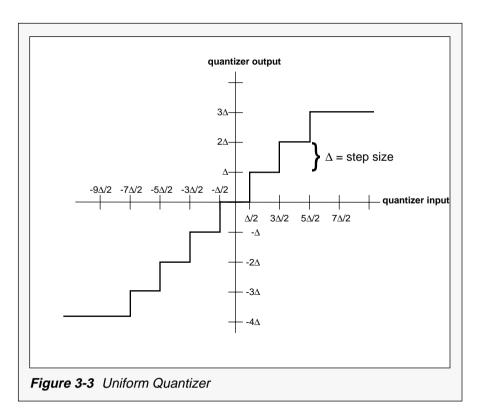

Figure 3-3 shows an example of a uniform quantizer. Uniform PCM quantizers feature a constant step size ( $\Delta$ ) [3]. To prevent large errors, the quantizer's range must represent the input signal's potentially maximum amplitude. The amount of noise that the quantizer introduces into the signal is also directly

related to the step size. Together, the quantizer range and the step size determine the number of bits required to adequately represent a signal of given quality. Telephone quality speech signals ("toll" quality) require about 35 dB of SNR in a frequency range of about 200-3200 Hz. Usually, 11-12 bits quantization at an 8 kHz sampling rate are needed to ensure this SNR over a typical range of speech signals [2].

## 3.2 Logarithmic PCM

One of the disadvantages of uniform PCM coding is that the SNR is not constant. For instance, during "voiced" segments of speech (vowels for example) the SNR may be high, but during "unvoiced" seqments of speech (consonants for example) the SNR may be low. Consequently, bits are wasted to ensure that the maximum SNR is always less than an acceptable level. Logically, if one can reduce the maximum SNR, then fewer bits will be needed. Non-uniform quantizers have features that aim to reduce the maximum SNR, including a step size that varies according to the input signal, or alternatively, non-uniform scaling of input before it is quantized [4]. With this approach, the step size is greater for large input amplitudes than it is for small amplitudes. The goal is to obtain a uniform SNR over all input ranges so that the SNR is independent of the input.

A basic approach to achieve this goal with speech signals is to logarithmically space the quantization levels. This approach, called logarithmic PCM (log PCM) coding, effectively compresses the input signal at the transmission end and expands it at the receiving end. For this reason, log PCM coding is also referred to as companding [4]. True logarithmic quantization is not practical in reality, but two methods that approximate this technique have been standardized [5]. These methods are referred to as  $\mu$ -law and A-law companding. They achieve a SNR that is constant enough for practical purposes. Compared with uniform PCM, these techniques

need about four fewer bits per sample for equivalent speech quality. Therefore, only eight bits are needed per sample rather than the 11 or 12 bits that uniform PCM needs. Eight-bit log PCM companding is one of the simplest forms of speech coding and has also been standardized for digital telecommunications.

Speech coders are typically specified in terms of bit rate. The bit rate is the number of samples per second, times the number of bits per sample. As noted, telephone quality voice signals primarily range from 200 to 3200 Hz and they are typically sampled at 8 kHz to maintain this frequency range. Therefore, the basic standard data rate for u-law and A-law PCM data is 8 bits/sample at 8000 samples/second or 64,000 bits/second (64 kbit/s). This is the source of the data rate for a basic digital transmission channel. The process of converting log PCM signals to/from analog signals is often done using CODEC devices (such as the MC145503). In the CCITT algorithm, the log PCM data is converted to linear PCM data before the ADPCM encoding itself is performed and the decoded linear signal is converted back into log PCM form after the decoding process is completed. The process for converting between log and linear PCM data, including the implementation on the DSP56001, is described in detail in the Motorola applications report "Logarithmic/Linear Conversion Routines For DSP56000/1" [6].

## 3.3 ADPCM Coding

Speech coders try to remove "redundancy" in speech signals in order to further reduce the data rate of speech signals obtained by PCM methods. Speech coders do this by taking advantage of known characteristics of speech signals. ADPCM is a technique of speech compression based on а combination of two basic speech coding techniques, Adaptive PCM (APCM) and Differential PCM (DPCM). A basic difference between these techniques versus uniform and log PCM methods is that they require previous samples to be remembered while uniform and log PCM methods do not. A second key difference is that uniform and log PCM coders have fixed compression and expansion curves (fixed step sizes), while most adaptive PCM methods change their compression and expansion curves over time (adaptive step sizes).

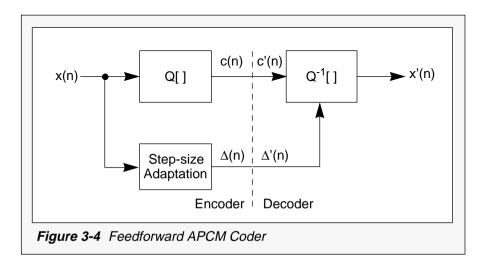

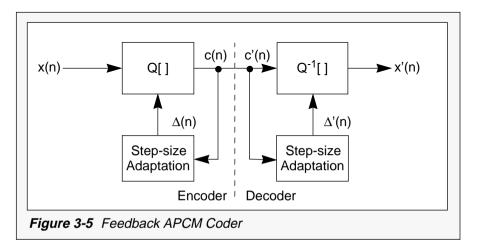

APCM coders take advantage of the tendency for speech signals to vary relatively slowly [2]. The coders exploit this property by changing the characteristics of the coder adaptively over time. One way to doing this is to change the quantizer step size in proportion to the average speech amplitude. The step size modification can be achieved in two ways; by either directly scaling the step size or by scaling the input signal by a gain factor. Updating the step size or gain factor can also be done in one of two ways. The feedforward approach, shown in Figure 3-4, actually sends the update information to the decoder over the transmission channel [7]. The feedback approach, shown in Figure 3-5, determines the information from the previously coded samples so that no extra information needs to be transmitted to the decoder [7]. APCM, in general, provides better SNR performance and speech quality at a given bit rate compared to uniform or log PCM but it does require more computation.

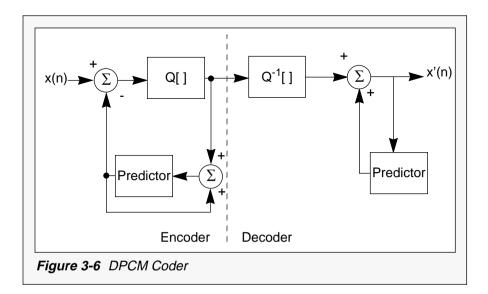

Other properties that are unique to speech signals relate to the spectral envelope. A typical short-time magnitude spectrum of a speech signal shows a slowly varying envelope whose shape is primarily determined by the vocal tract response. This causes speech samples to have a high degree of "sample-to-sample correlation" [2]. DPCM techniques try to take advantage of this characteristic. DPCM coders are characterized by the use of a predictor that forms an estimate of each incoming speech sample. This estimate is subtracted from the actual sample and the difference between them is coded instead of the actual input sample. Most DPCM coders use a form of linear prediction where the estimate is based on a linear combination of previous input samples. A block diagram of a DPCM coder is shown in Figure 3-6 [2].

MOTOROLA

ADPCM techniques use a combination of APCM and DPCM techniques. There are many different ways to implement the concepts of APCM and DPCM. Therefore, the term ADPCM can justifiably refer to a broad range of speech coders that may have widely varving characteristics. ADPCM as well as APCM and DPCM techniques. techniques, may also be applied to non-speech signals, such as high-fidelity audio signals or video images. These implementations may not exploit properties that are specific to speech, however. The term ADPCM as used in this discussion refers specifically to the algorithm defined by the CCITT for telephone quality speech signals. Therefore the scope of this algorithm may not apply to all applications requiring signal compression. A general block diagram of the ADPCM configuration used in the CCITT algorithm is shown in Figure 3-7 [2].

#### **SECTION 4**

## The CCITT ADPCM Algorithm

"The decoder portion of the CCITT algorithm uses the same routines as the encoder for the inverse quantization, linear prediction, tone detection, and adaptation functions." The CCITT ADPCM coder is designed to meet several specific requirements [8]. The design goals were to:

- provide compression while satisfying the objective signal quality requirements specified in CCITT Recommendation G.712 [10]

- retain a high enough level of subjective quality (defined by listening tests) even after a series of encodings and decodings

- $\bullet$  provide compatibility with the existing  $\mu\mbox{-law}$  and A-law PCM formats

- operate stably in the presence of high-bit-error rates during transmission

- operate properly in the presence of voiceband data at up to 4.8 kbit/s

These requirements and others led to the standardization of this particular algorithm. The following paragraphs provide an overview of this algorithm, followed by a detailed description of each part. This application report focuses on the algorithm implementation rather than the complete development of the theory behind this algorithm. A detailed block diagram of the encoder portion of the CCITT ADPCM algorithm is shown in Figure 4-1. The decoder portion is shown in Figure 4-12. The algorithm uses the feedback method whereas the encoder uses only the coded ADPCM signal I(k) for feedback to the prediction and adaptation sections. Since this information is the same that the decoder uses for adaptation, no update parameters need to be sent over the transmission channel. This structure has two key properties:

- 1. The encoder and the decoder are almost functionally identical.

- 2. The decoder is in the same "state" as the encoder for a given sample (assuming no transmission errors).

Therefore, all common internal signals are identical, enabling the decoder to keep track of the encoder's adaptive process without explicitly receiving information from the encoder.

The APCM portion of the algorithm uses the gain factor approach for quantization. The difference signal to be coded is first scaled by the adaptive scale factor y(k) before it is quantized according to a fixed quantization curve. The smallest step size allowed by the overall quantization is equivalent to the smallest step size defined in  $\mu$ -law or A-law PCM. The largest step size is 1024 times the smallest step size. It should be noted that the gain factor itself and other signals used in its computation are in base 2 logarithmic form. The adaptation of the scale factor y(k) is based on a "bimodal" adaptation technique (the quantizer is also called a dynamic locking quantizer). The scaling adaptation rate is "fast" for signals with large fluctuations, like speech, and is "slow" for signals with small fluctuations, like voiceband data and tones. A purely stationary input such as a single tone causes the quantizer to stop adapting or to "lock". The overall speed of adaptation is a combination of the fast (unlocked) and slow (locked) scale factors.

The DPCM portion of the algorithm uses a linear predictor that is based on an autoregressive moving average (ARMA) process which has a combination of poles and zeros in its transfer function [4]. The structure for the predictor is based on several factors including stability in the presence of errors and the ability to track both speech and voiceband data signals. The adaptation of the predictor coefficients is based on a gradient search or steepest descent method and all coefficients are updated for each input sample. The output of the linear predictor is the signal estimate  $s_e(k)$ . This signal is subtracted from the input signal to form the difference signal that is actually coded and sent to the decoder.

The additional blocks added to the CCITT coder are for PCM format conversion, tone transition detection. and synchronization. The tone transition detection determines when transitions between stationary tone signals occur. When a transition is detected all of the coefficients in the predictor are set to zero and the quantizer is set to the fast (unlocked) mode. The synchronization block helps prevent noise accumulation PCM/ADPCM/PCM when multiple conversions (synchronous tandem codings) are performed on a signal. This synchronization block does not affect the internal state of the decoder and has a minimal effect on the output quality of a single PCM/ADPCM/PCM conversion

### 4.1 The Encoder Algorithm

Figure 4-1 shows a block diagram of the major portions of the CCITT ADPCM encoder. This section gives a detailed description of each block. The DSP56001 assembly code routines associated with each block are described in detail in **SECTIONS 5.2 and 5.3**. The first stage of the encoder is shown in Figure 4-2. The input to the encoder is the A-law or  $\mu$ -law PCM signal s(k). This signal is converted to a uniform (linear) PCM signal s<sub>I</sub>(k) in the routine EXPAND. In the next routine, SUBTA, the difference signal d(k) is calculated by subtracting the signal estimate s<sub>e</sub>(k) from s<sub>I</sub>(k). As in all DPCM type coders, the difference signal is actually encoded and transmitted rather than a compressed version of the input signal.

Ean. 4-1

$$d(k) = s_{l}(k) - s_{e}(k)$$

In the next stage of the encoder, shown in Figure 4-3, the difference signal d(k) is quantized by a 15-level non-uniform adaptive quantizer. The quantization process is performed by three routines. In the routine LOG the linear difference signal d(k) is converted to a base 2 logarithmic form, d<sub>l</sub>(k) representing the magnitude, and d<sub>s</sub>(k) representing the sign. The scale factor y(k) (also in logarithmic form) is then subtracted from d<sub>l</sub>(k) in the routine SUBTB, in effect dividing the linear signal d(k) by a gain factor. This normalized

signal  $d_{ln}(k)$  is then quantized in the routine QUAN according to the normalized input/output characteristic shown in Table 4-1.

| Table 4-1Quantizer Normalized Input/OutputCharacteristic |      |                                            |

|----------------------------------------------------------|------|--------------------------------------------|

| INPUT                                                    |      | OUTPUT                                     |

| log2 d(k) -y(k)                                          | l(k) | log <sub>2</sub>  d <sub>g</sub> (k) -y(k) |

| [3.12, +∞)                                               | 7    | 3.32                                       |

| [2.72, 3.12)                                             | 6    | 2.91                                       |

| [2.34, 2.72)                                             | 5    | 2.52                                       |

| [1.91, 2.34)                                             | 4    | 2.13                                       |

| [1.38, 1.91)                                             | 3    | 1.66                                       |

| [0.62, 1.38)                                             | 2    | 1.05                                       |

| [-0.98, 0.62)                                            | 1    | 0.031                                      |

| (-∞, 0.98)                                               | 0    | -∞                                         |

The output of the quantizer section is the 32-kbit/s ADPCM signal I(k). This is the overall output of the encoder that is transmitted to the decoder. Each sample of I(k) contains four bits, three bits for the magnitude (from Table 4-1) and one bit for the sign (from  $d_s(k)$ ). The quantizer is a 15-level quantizer since the all-zero codeword is not allowed.

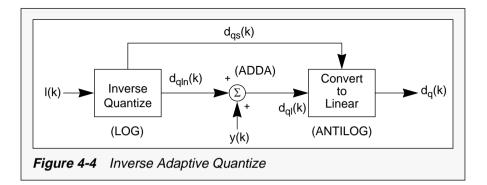

The inverse adaptive quantizer, shown in Figure 4-4, converts the ADPCM signal I(k) into the signal dq(k), the quantized version of the difference signal. The inverse quantization is performed in three routines that are effectively the inverse of the three quantizer routines. The routine RECONST maps the magnitude of I(k) into one of eight normalized output values shown in Table 4-1. The routine ADDA adds the scale factor y(k) (the same value as in the quantizer) to the normalized output value d<sub>qln</sub>(k), in effect multiplying by a gain factor. The routine ANTILOG then converts this logarithmic value d<sub>ql</sub>(k), along with the sign of I(k) (d<sub>qs</sub>(k)), to the linear quantized difference signal d<sub>q</sub>(k).

The remaining portion of the encoder performs three main functions:

- 1. calculating the new signal estimate

- 2. performing the adaptation functions

- 3. detecting tones

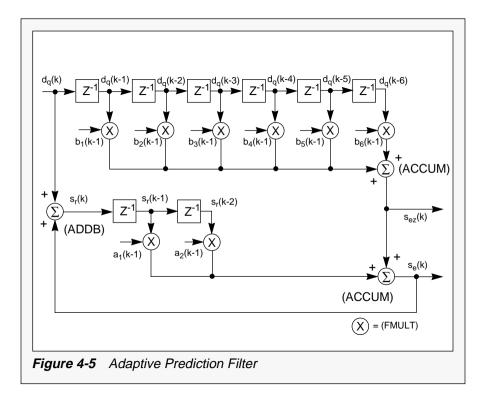

The adaptive predictor's primary function is to use the past history of the quantized difference signal  $d_q(k)$  to update the signal estimate  $s_e(k)$ . The linear predictor model used for the prediction consists of a sixth order section that models zeroes and a second order section that models poles. The prediction filter shown in Figure 4-5, is implemented in the routines FMULT and ACCUM using the equations:

$$s_{ez}(k) = \sum_{i=1}^{6} b_i(k-1) \bullet d_q(k-i)$$

Eqn. 4-2

$$s_{e}(k) = \sum_{i=1}^{2} a_{i}(k-1) \bullet s_{r}(k-i) + s_{ez}(k)$$

Eqn. 4-3

The CCITT standard specifies that the multiplies in Eqn. 4-2 and Eqn. 4-3 be done in floating point so the values of  $d_q(k)$  and  $s_r(k)$  must be converted to floating point. This is done in the routines FLOATA and FLOATB. The signal  $s_r(k)$  in Eqn. 4-2 and Eqn. 4-3 is the reconstructed signal. The routine ADDB calculates  $s_r(k)$  by adding the quantized difference signal  $d_q(k)$  to the signal estimate  $s_e(k)$  as shown in Eqn. 4-4. The reconstructed signal represents the overall output of the ADPCM algorithm. The encoder does not output this signal but uses it as feedback for the prediction.

$$s_{r}(k-i) = s_{e}(k-i) + d_{a}(k-i)$$

Eqn. 4-4

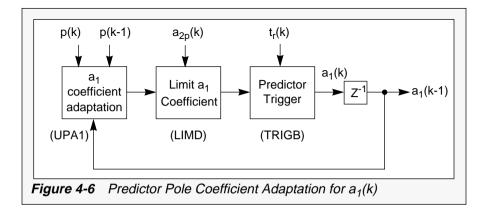

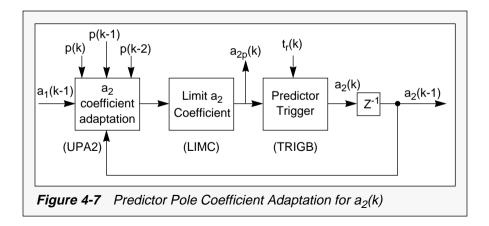

The predictor coefficients  $a_i(k)$  and  $b_i(k)$  are updated for each sample using a gradient search algorithm. The adaptation of the two pole coefficients,  $a_1(k)$  and  $a_2(k)$  is shown in Figure 4-6 and Figure 4-7 respectively. These coefficients are updated according to the following equations:

$$a_1(k) = (1 - 2^{-8})a_1(k-1) + (3 \cdot 2^{-8})sgn[p(k)]sqn[p(k-1)]$$

Eqn. 4-5

$$a_{2}(k) = (1 - 2^{-7})a_{2}(k-1) + 2^{-7}(sgn[p(k)]sgn[p(k-2)]$$

Eqn. 4-6

-f[a\_{1}(k-1)]sgn[p(k)]sgn[p(k-1)])

where:

$$p(k) = d_{q}(k) + s_{ez}(k)$$

Eqn. 4-7

Eqn. 4-5 is implemented in the routine UPA1 while Eqn. 4-6 and Eqn. 4-8 are implemented in the routine UPA2. Eqn. 4-7 is calculated in the routine ADDC. The coefficients  $a_1(k)$  and  $a_2(k)$  are constrained for stability reasons to the following limits:

| a <sub>2</sub> (k) | ≤ 0.75                                    | Eqn. 4-9  |

|--------------------|-------------------------------------------|-----------|

| a <sub>1</sub> (k) | ≤ 1 - 2 <sup>-4</sup> -a <sub>2</sub> (k) | Eqn. 4-10 |

Eqn. 4-9 is calculated in the routine LIMC and Eqn. 4-10 is calculated in the routine LIMD.

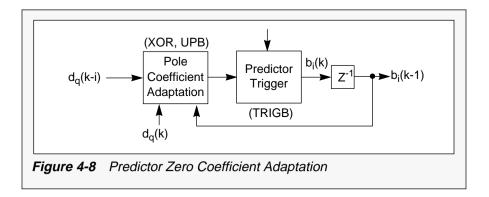

The adaptation of the  $b_i(k)$  zero coefficients is shown in Figure 4-8. They are updated in the routines XOR and UPB according to:

$$b_i(k) = (1 - 2^{-8}) b_i(k - 1) + 2^{-7} sgn[d_q(k)] sgn[d_q(k-i)]$$

for i = 1,2,...,6 Eqn. 4-11

The  $b_i(k)$  coefficients are implicitly limited to  $\pm 2$ .

The function sgn[x] in Eqn. 4-5 through represents the sign of x. It is defined as:

The predictor coefficients may be further modified by the tone transition signal  $t_r(k)$ . The routine TRIGB tests  $t_r(k)$  for a transition detection and sets the predictor coefficients to 0 if a transition is detected.

If

$$t_r(k) = 1$$

then  $a_i(k) = b_i(k) = t_d(k) = 0$  Eqn. 4-13

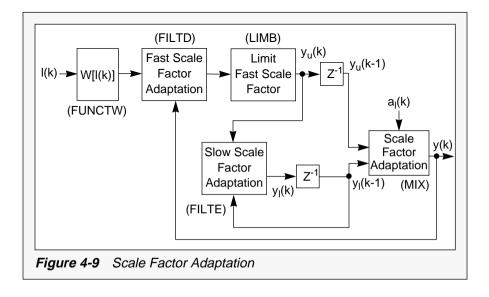

The adaptation of the scale factor y(k) is based on information from past values of I(k) and the speed

control parameter  $a_l(k)$ . The overall speed of adaptation is a combination of the fast and slow scale factors  $y_u(k)$  and  $y_l(k)$ . The speed control parameter  $a_l(k)$  determines how the fast and slow scale factors are combined. A diagram of this process is shown in Figure 4-9.

The fast (unlocked) scale factor  $y_u(k)$  is calculated in the routine FILTD equation:

$y_{ij}(k) = (1 - 2^{-5}) y(k) + 2^{-5} W[I(k)]$  Eqn. 4-14

The routine LIMB constrains  $y_u(k)$  to the limits:

$$1.06 \le y_u(k) \le 10.00$$

Eqn. 4-15

The function W(I) according to Eqn. 4-14 is calculated in the routine FUNCTW according to Table 4-2.

| Table 4-2         W(I) Lookup Table |       |       |       |      |      |      |      |       |  |  |

|-------------------------------------|-------|-------|-------|------|------|------|------|-------|--|--|

| l(k)                                | 7     | 6     | 5     | 4    | 3    | 2    | 1    | 0     |  |  |

| W(I)                                | 70.13 | 22.19 | 12.38 | 7.00 | 4.00 | 2.56 | 1.13 | -0.75 |  |  |

The slow (locked) scale factor  $y_l(k)$  is calculated in the routine FILTE by the equation:

$$y_{l}(k) = (1 - 2^{-6}) y_{l}(k-1) + 2^{-6} y_{u}(k)$$

Eqn. 4-16

The overall scale factor y(k) is determined in the routine MIX by the equation:

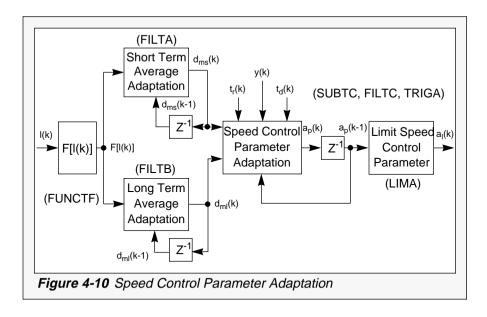

The speed control parameter  $a_l(k)$  is limited to the range  $0 < a_l(k) < 1$ . The value of  $a_l(k)$  approaches 1 for speech signals in which case the fast (unlocked) scale factor  $y_u(k)$  dominates in Eqn. 4-17. For data signals and tones however, the value of  $a_l(k)$  approaches 0 in which case the slow (locked) scale factor  $y_l(k)$  dominates in Eqn. 4-17. The value of  $a_l(k)$  is determined primarily by the rate-of-change of the difference signal, which is encoded in l(k). The update of  $a_l(k)$  is shown in Figure 4-10.

Two measures of the difference signal value are used to update the speed control parameter,  $d_{ms}(k)$ and  $d_{ml}(k)$ . The signal  $d_{ms}(k)$  represents the "short term" average of the function F[I(k)], while  $d_{ml}(k)$ represents the "long term" average of F[I(k)]. The value of F[I(k)] is a weighted function of I(k) and is determined in the routine FUNCTF according to Table 4-2. The difference signals  $d_{ms}(k)$  and  $d_{ml}(k)$  are calculated in the routines FILTA and FILTB respectively according to the equations:

$$\begin{aligned} &d_{ms}(k) = (1 - 2^{-5}) d_{ms}(k-1) + 2^{-5} F[I(k)] & \text{Eqn. 4-18} \\ &d_{ml}(k) = (1 - 2^{-7}) d_{ml}(k-1) + 2^{-7} F[I(k)] & \text{Eqn. 4-19} \end{aligned}$$

The values of  $d_{ms}(k)$  and  $d_{ml}(k)$  are used to determine the "unlimited" speed control parameter  $a_p(k)$ . The value of  $a_p(k)$  is calculated in the routines SUBTC, FILTC, and TRIGA by the equation:

| $a_p(k) = (1-2^{-4})a_p(k-1) + 2^{-3}$ | $\text{if }  d_{ms}(k)\text{-}d_{ml}(k)  \geq 2^{\text{-}3}d_{ml}(k)$ |           |

|----------------------------------------|-----------------------------------------------------------------------|-----------|

| $= (1-2^{-4})a_{p}(k-1) + 2^{-3}$      | if y(k) < 3                                                           |           |

| $= (1-2^{-4})a_{p}(k-1) + 2^{-3}$      | if $t_d(k) = 1$                                                       |           |

| = 1                                    | if $t_r(k) = 1$                                                       | Eqn. 4-20 |

| $= (1-2^{-4})a_{p}(k-1)$               | otherwise                                                             |           |

The value of  $a_p(k)$  tends towards 2 if the difference between  $d_{ms}(k)$  and  $d_{ml}(k)$  is large, indicating the rate-of-change of the difference signal is fast, but it tends towards 0 if the difference is small, indicating the rate-of-change is slow. The value of  $a_p(k)$  also tends towards 2 when tones are detected ( $t_d(k) = 1$ ) or in idle channel conditions (y(k) < 3). When a tone transition is detected ( $t_r(k) = 1$ ), explicitly set to 1.

|         |   | Tal | ole 4-3 | F[l(k)] Lo | ookup Ta | able |   |   |

|---------|---|-----|---------|------------|----------|------|---|---|

| l(k)    | 7 | 6   | 5       | 4          | 3        | 2    | 1 | 0 |

| F[l(k)] | 7 | 3   | 1       | 1          | 1        | 0    | 0 | 0 |

To form the desired speed control parameter  $a_l(k)$  the parameter  $a_p(k)$  is constrained in the routine LIMA to the limits given in . This limiting has the effect of delaying a state transition start until the magnitude of the difference signal become relatively constant.

$$\begin{array}{ll} a_i(k) & = 1 & \mbox{if } a_p(k{\text{-}}1) > 1 \\ & = a_p(k{\text{-}}1) & \mbox{if } a_p(k{\text{-}}1) \leq 1 \end{array} \qquad \qquad \mbox{Eqn. 4-21} \end{array}$$

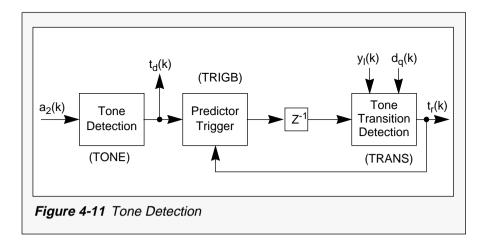

The final step of the encoder is tone detection, shown in Figure 4-11. It is included to improve the performance of the coder in the presence of non-speech voice-band data signals that may be present on a typical analog phone line (e.g. DTMF tones and data modems.) The tone detect signal,  $t_d(k)$ , indicates the presence of a tone. When a tone is detected,  $t_d(k)$  causes the quantizer to be driven into the fast mode of adaptation. The TONE routine calulates  $t_d(k)$  by the equation:

$$t_d(k) = 1$$

if  $a_2(k) < -0.71875$

= 0 otherwise Eqn. 4-22

The tone detect signal,  $t_d(k)$ , also causes the tone transition detect signal,  $t_r(k)$ , to be set when a transition between tones occurs. This signal sets the predictor coefficients to 0 and the tone detect signal to 0 (in the TRIGB routine) so that the fast adaptation mode will take effect immediately. The tone transition detect signal,  $t_r(k)$  is determined in the routine TRANS by the equation:

$t_r(k) = 1$  if  $a_2(k) < -0.71875$  and  $|dq(k)| > 24 \cdot 2 y_i(k)$  Eqn. 4-23 = 0 otherwise

## 4.2 The CCITT Decoder Algorithm

A detailed block diagram of the decoder process is shown in Figure 4-12. As mentioned previously, the CCITT ADPCM coder uses the feedback scheme and one of the properties of this scheme is that the encoder and decoder are almost identical in terms of function. The decoder portion of the CCITT algorithm uses the same routines as the encoder for the inverse quantization, linear prediction, tone detection, and adaptation functions. The input to the decoder, I(k), is the same I(k) used in the encoder for adaptation and prediction. The decoder executes all of the same routines as the encoder (and in the same order) except for the input PCM conversion (EXPAND), the difference signal computation (SUBTA), and the adaptive quantization (LOG, SUBTB, and QUAN). These sections are normally not needed in the decoder but they are used in the

CCITT algorithm however, as explained in the following paragraphs.

The linear output of the decoder is the reconstructed signal  $s_r(k)$  as calculated in the routine ADDB. This is converted to the A-law or  $\mu$ -law PCM signal  $s_p(k)$  in the routine COMPRESS. This would normally be the final output but instead this signal is passed through a synchronous coding adjustment block, shown in Figure 4-13. The purpose of this block is to prevent cumulative distortions that may occur with "synchronous tandem codings" - multiple ADPCM/PCM/ADPCM conversions on a transmission path. These distortions can only be prevented when the transmission paths are error-free and when no extra digital signal processing functions are performed on intermediate PCM and ADPCM signals.

As noted previously, the encoder and decoder will be in the same internal "state" (all internal variables the same) assuming there are no transmission errors. The decoder then estimates the quantization that occurred in the encoder and forces the ADPCM sequence which it reconstructs to match the ADPCM sequence which it received. The decoder does so by converting the PCM signal  $s_p(k)$  back to a linear signal  $s_{lx}(k)$  in the EXPAND routine. A new difference signal  $d_x(k)$  is then calculated in the SUBTA routine by the equation:

$$d_{x}(k) = s_{lx}(k) - s_{e}(k)$$

Eqn. 4-24

The new difference signal  $d_x(k)$  is then converted to the normalized logarithmic signal  $d_{lnx}(k)$  in the routines LOG and SUBTB. The same quantization as in the encoder then occurs in the routine SYNC. But this routine also does a comparison of the new coded ADPCM signal to the received ADPCM signal l(k). The final PCM output of the decoder,  $s_d(k)$ , is determined by this comparison, defined by:

| $s_d(k) = s_p(k)^+$               | if $d_{x}(k) < lower interval boundary$      |

|-----------------------------------|----------------------------------------------|

| = s <sub>p</sub> (k) <sup>-</sup> | if $d_{\chi}(k) \ge upper$ interval boundary |

| $= s_p(k)$                        | otherwise                                    |

Eqn. 4-25

#### where:

- *s<sub>p</sub>(k)+ = the PCM code word that represents the next more positive PCM output level*

- *s*<sub>p</sub>(*k*)- = the PCM code word that represents the next more negative PCM output level

### **SECTION 5**

# ADPCM Implementation on the DSP56001

"The standard version of the DSP56001 ADPCM source code implements the ADPCM algorithm exactly as specified by the CCITT." **T** wo versions of the CCITT ADPCM algorithm described in previous sections have been implemented on the DSP56001, both in a full-duplex configuration. The assembly source code for these programs are available on the Motorola DSP bulletin board (Dr. BuB) under the names ADPCM.ASM and ADPCMNS.ASM. The code for the standard version is provided in a form that will process data in files on a host computer. The non-standard version is set up for real-time operation. The I/O interface to either version can be easily modified for other configurations.

The program that implements the standard version, ADPCM.ASM, has been optimized. This optimization enables it to perform both the encode and the decode portions of the algorithm in real-time on a single DSP56001, running at 27 MHz with external program memory. The source code is set up to run the CCITT test sequences specified in Appendix II of Recommendation G.721 (1986 version) [1]. This code is a bit-for-bit compatible implementation of the CCITT specification and correctly passes all µ-law and A-law test sequences provided by the CCITT. ADPCMNS.ASM is the program for the non-standard version and it is a modification of the standard implementation. ADPCMNS.ASM performs the complete ADPCM algorithm in real-time on a single DSP56001, and requires less computational power than the standard version. In addition to providing a more efficient implementation of the ADPCM algorithm, this version is better suited for modification since the algorithm is programmed more directly than the CCITT standard specification allows.

For both ADPCM versions, the encoder and decoder portions of the source code are designed to be independent of the I/O interfaces so that the code can be easily modified for a variety of configurations, including single or multiple channel half-duplex configurations. For the standard version, this feature permits real-time performance on a slower speed DSP56001 or allows other simultaneous tasks to be performed on the same 27 MHz DSP56001. For the non-standard version, this feature allows an even greater variety of configurations. Further performance details for both described SECTION versions are in 5.5 Performance Specifications. This section details the implementation of the CCITT ADPCM algorithm on the DSP56001.

This application report provides only a basic description of the source code. For a more complete understanding of the DSP56001 code, refer to the CCITT document. Many of the details in Recommendation G.721 are not included in this document but have a significant impact on the assembly implementations, especially the standard version. In many cases, the standard code does not implement the equations given in this document in a straightforward manner due to the way the specification is written. Also, many of the comments in the source code refer to the notations used in Recommendation G.721. (See **APPENDIX A Terminology** for definitions of the basic terminology).

## 5.1 I/O Interface

The standard ADPCM source code is set up to run the CCITT test sequences on the Motorola DSP56000ADS board. The program simulates the PCM and ADPCM interfaces by using the file I/O routines on the ADS board. The file I/O routines allow programs running on the ADS board to access data in ASCII files on the host computer. These routines provide a convenient method for accessing the CCITT test files which are distributed in ASCII format. The ADS does require that the data in the test files be in a slightly different format than that provided by the CCITT. The details of this format can be found in the file ADPCM.HLP located with the ADPCM source code on the Motorola DSP bulletin board. The source code is set up to process a PCM input file to test the encoder and an ADPCM input file to test the decoder simultaneously. Two output files are written, one for the encoded ADPCM output and one for the decoded PCM output. When running the CCITT test sequences these output files can be compared to the CCITT files to verify correct operation. This procedure is

also discussed in the ADPCM.HLP file. The data in the two files being processed does not have to be related in any way since the encoder and decoder are designed to operate on two independent signals. Additionally, any file containing PCM data in ASCII hex characters may be used as input to the encoder, and likewise any file containing ADPCM data can be used as input to the decoder. It should be noted however that the file I/O routines on the ADS are not designed for high-speed data transfer so that processing data files with the DSP56001 ADPCM program will not be in real-time.

The non-standard ADPCM program includes the code required for a real-time I/O interface. The PCM channel is provided by a Motorola MC145503 CODEC connected to the DSP56001's Synchronous Serial Interface (SSI). Eight general-purpose I/O pins on the DSP56001 are used for the ADPCM channel. Four are used for parallel input and the other four are used for parallel output.

The SSI interface (both the transmit and receive) and the parallel I/O interface are assumed to be synchronous. The code is synchronized with the I/O interface by polling. No interrupts are used, although they can be added if desired. The real-time full-duplex operation of the non-standard ADPCM program has been tested on a set-up consisting of two DSP56000ADS. Further details of this test setup can be found in the file ADPCMNS.HLP.

As mentioned previously, the I/O interface of the ADPCM programs are designed to be flexible for a variety of configurations. The standard ADPCM

code is provided with a file I/O interface to allow easy testing of the CCITT sequences, but it can be easily modified for a real-time interface. This was done to test the real-time operation of the algorithm. Only the interface portion of the source code was changed. The algorithm itself was not modified. The non-standard code already contains code for a realtime interface, but it can be modified for other configurations as well. In addition to the test set-up using CODECs for the PCM channel, this code was tested with a 16-bit linear A/D and D/A interface. In this case the PCM compression and expansion routines were removed, but again the algorithm itself was not modified.

### 5.2 Standard Implementation

The standard version of the DSP56001 ADPCM source code implements the ADPCM algorithm exactly as specified by the CCITT. The advantage of using this version is that the user can be confident that the DSP56001 implementation will perform exactly as specified by the CCITT. This includes performance with non-speech signals and in special operating conditions. The disadvantage of this version is that the specification does not always allow the equations to be implemented in an efficient manner on a general purpose digital signal processor. An example is the multiply and accumulation portion of the linear predictor. The standard specifies that the multiply be done in a floating-point

format while the accumulation be done in 16-bit fixed point format. Not only is the floating-point multiply less efficient than a native 24-bit fixed point multiply on the DSP56001, but several conversions between fixed and floating-point formats are required for each sample (see **SECTION 5.2.5 Floating-Point Conversion**). This is the most time consuming part of the algorithm but other parts of the specification also do not permit efficient implementation on a programmable microprocessor.

The standard implementation was written with the following two objectives:

- to adhere with the CCITT specification in order to maintain bit-for-bit compatibility with the CCITT test sequences

- to obtain a full-duplex solution with real-time operation on a single DSP56001

Knowing that the standard version was written with these two primary objectives may help to clarify the way the algorithm was implemented.

#### 5.2.1 Code Structure

The assembly program for the standard version of the ADPCM algorithm is structured as two main routines, the encoder (transmit) and the decoder (receive), plus one subroutine for initialization. After the initialization routine, the encoder routine is executed, followed by the decoder. The code then alternates between the encoder and decoder indefinitely. A flow diagram of the encoder and decoder is shown in Figure 5-1. This shows the order in which the various portions of the algorithm are executed. The order of execution of the individual CCITT routines along with their execution speed is given in **SECTION 5.4 Performance Specifications**.

The encoder and decoder routines are designed to operate as independent code segments. They do assume that appropriate variables are stored in data memory and that appropriate pointers have been set. In particular, address registers r1, r2, r6, and r7 should contain the appropriate memory addresses prior to executing the encoder and decoder sections. Registers r3 and r5 should contain constant address values used for table lookup. Registers r0 and r4 do not need to be initialized since they are used as general purpose registers. The encoder and decoder are not set up as subroutines in the program. If interrupts are used for data I/O, they can easily be made into subroutines or interrupt routines. However, one routine should not interrupt the other routine until it is completely finished executing.

No subroutines are used within the encoder or the decoder so that optimal speed can be obtained. The code has also been optimized to take advantage of the DSP56001's architecture as much as possible. This causes the various CCITT routines in the code to "overlap" in many cases, meaning that variables and data values for one routine may be read from memory while the previous routine is still executing. In one case, the XOR and UPB routines are actually combined into a single section of code.

This optimization makes the code more difficult to follow in some cases, however, extra comments were added to clarify most of these cases. Further discussion of this optimization technique is presented in **SECTION 5.4 Optimization Techniques**.

#### 5.2.2 Initialization

The initialization subroutine accomplishes three main tasks:

- 1. initializing the DSP56001

- 2. initializing program variables and lookup tables

- 3. initializing data buffer pointers and modulo registers

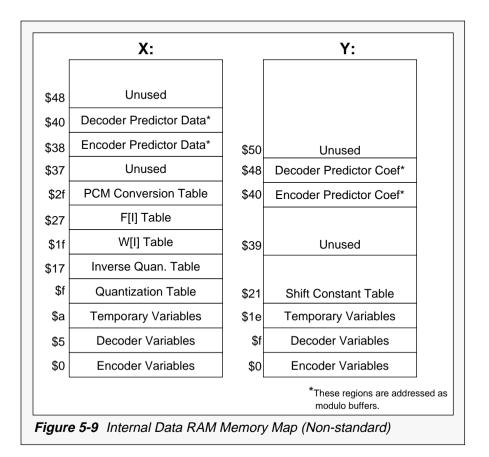

This subroutine also includes any I/O interface configuration that is necessary. Figure 5-2 shows the memory map of the internal data RAM. The encoder and decoder algorithms each require several variables to be stored in memory. The DSP56001 code also requires several other temporary storage locations. Most of the variables used by the algorithm are stored in data memory below address \$40 so that the short immediate addressing mode can be used when accessing them. Data locations that are accessed with an addressing register are stored at higher locations in data memory since they do not need to use immediate addressing modes.

The DSP56001 initialization consists of enabling the on-chip, factory programmed data ROM tables and setting the DSP56001's Bus Control Register (BCR) for zero wait state external program memory access. The  $\mu$ -law and A-law ROM table in X memory is

needed for the log PCM conversion routine. The zero wait states for external program memory are needed so the algorithm will run in real time.

The program initialization is done in the subroutine INIT, First, all internal X and Y data RAM is cleared. all variables that require specific values are initialized. and then all lookup tables are copied from their loadtime locations in program memory to their run-time locations in data RAM. Next, the pointers to the receive (decode) and transmit (encode) data buffers are initialized. These buffers hold the delayed values of  $d_{\alpha}(k)$  and  $s_{r}(k)$  used in the linear predictor filter. These are the only true modulo buffers used in the assembly code in the sense that the newest delayed values replace the oldest delayed values without actually moving the other delayed values. The INIT routine initializes the sign and mantissa locations in these buffers since the code assumes a certain range of legal values in these locations. The INIT routine also initializes other variables including the variable LAW. It determines whether the µ-law or A-law format is chosen. The program defaults to setting LAW to zero to select u-law for the PCM format. The code can be changed to set LAW to any non-zero value which will select the A-law format. It can also be easily modified to select µ-law or A-law based on an external input.

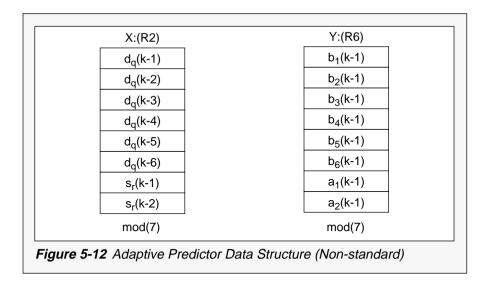

The remaining portions of the INIT routine initialize the addressing registers and modifier registers that are used to access the data memory. Six of the variable storage areas (indicated by \* in Figure 5-2) are addressed using modulo pointers. These six areas, three each for the encoder and decoder, are used by the linear predictor filter.

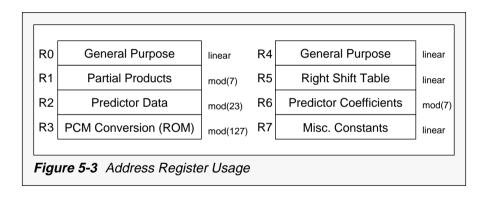

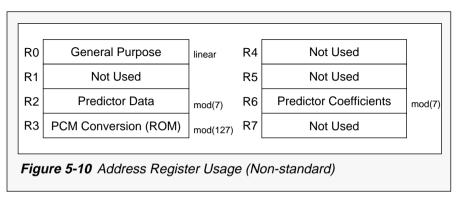

The complete addressing register assignments along with the associated addressing modes are shown in Figure 5-3. Six of the addressing registers are reserved for particular functions, and the remaining two are used for other general purpose tasks requiring addressing registers. The INIT routine can also contain any initialization needed for a hardware interface such as the SSI port. No initialization is needed to use the file I/O routines on the ADS so I/O initialization is not included in the standard code.

#### 5.2.3 PCM Format Conversion

The ADPCM algorithm uses several different types of numeric formats. Conversion between these formats is required in several places in the assembly code. The log PCM format conversion is one of these instances. Two different routines are used for converting between µ-law or A-law PCM samples and linear (uniform) samples. EXPAND converts an

8-bit log PCM sample to a linear 14-bit two's-complement representation that is suitable for numeric operations. COMPRESS performs the opposite conversion. The DSP56001 ADPCM implementation supports both  $\mu$ -law and A-law format conversion.

The routine EXPAND performs the conversion by using the internal u-law and A-law ROM tables on the DSP56001. EXPAND uses register r3 as the pointer into the lookup table. Register r3 is set during program initialization to either the u-law table base or the A-law table base and remains set to this value while the program is running. Register n3 is used as an offset into the ROM table. The assembly code for EXPAND is identical for both formats and is only dependent on the base pointer stored in r3 so separate routines are not needed. To obtain optimal speed, the COMPRESS routine requires separate code sections for the µ-law and A-law conversion. In this routine, the variable LAW is tested for each sample. If only one format is used. the variable LAW may be eliminated and one section of COMPRESS may be removed to save program memory. The SYNC routine discussed in SECTION 5.2.11 also requires separate code segments for each log PCM format, so similar program memory savings can be obtained there.

The EXPAND and COMPRESS routines are modified versions of routines given in the Motorola applications brief "Logarithmic/Linear Conversion Routines for the DSP56000/1" [6]. They were chosen based on maximum execution speed. Complete descriptions of each routine can be found in the above applications brief.

#### 5.2.4 Logarithmic Conversion

Another conversion required in the ADPCM algorithm is between a linear and a base 2 logarithmic format. The quantizer and the inverse quantizer achieve their adaptive characteristic by use of a scale factor. The scale factor itself and many of the variables used to calculate it are in a base 2 logarithmic form. The total number of bits used for these variables differs but they all share a common form of a mixed number. The numeric operations are performed on these numbers assuming an integer exponent portion combined with a fractional mantissa portion in one mixed number. The scale factor adaptation does not require a specific conversion to this format but a conversion is required in the guantizer and inverse quantizer. The routine LOG in the quantizer converts the difference signal to the base 2 logarithmic form so that it can be modified by the scale factor. In the inverse quantizer, the routine ANTILOG converts the quantized difference signal back to the linear form after it has been readjusted by the scale factor. In fact, the ADPCM codeword is based on the log of the difference signal d(k) rather than the difference signal itself.

Figure 5-4 illustrates the conversion process in a version of the LOG routine. The input D is in a 16-bit two's complement format. The first step is to convert this number to a sign magnitude representation saving the sign in register y1. After checking the magnitude for a non-zero value it is then normalized to determine the exponent and mantissa. The iterative NORM instruction is used for this conversion. This instruction will shift the magnitude left one bit for each iteration until a 0 is in bit 23 and a 1 is in bit 22 (this is the normalized fraction format on the DSP56001). For each left shift the value in r0 is decremented. Once the magnitude has been normalized successive iterations will do no further adjustments. Fourteen iterations are performed since the maximum that the magnitude can be shifted is 14 bits, assuming the magnitude is non-zero. Fourteen iterations of the NORM is not needed in all cases but taking time to test after each iteration would cause the worst case delay to be longer. After the normalization process is finished the normalized mantissa will be in accumulator *a* and the associated exponent will be in register r0.

The remaining instructions combine the exponent and mantissa into a mixed number. The truncation of the mantissa to seven bits is performed by using a mask instead of actually shifting. This technique is common throughout the code. The process of combining the exponent and mantissa also shows the technique of shifting by multiplication. The exponent is moved from r0 to x1 where it will be in the four LSBs but it needs to be left justified to bits 22-19 which are the four MSBs of the DSP56001's fractional format. A shift constant is read from the shift constant table in Y memory and is multiplied with the exponent. The result is that the exponent is effectively shifted left 19 bits. A shift constant is also used to shift the mantissa right by three bits. In this example the mantissa is shifted right and combined with the exponent in a single MAC instruction. This shift technique is described in further detail in SECTION 5.4. The resulting log signal DL is a mixed number with

four integer bits and seven fractional bits with an implied radix point. Note that this logarithmic format is similar to the mixed number format discussed in [9].

```

LOC

.

:

; Convert difference signal from the linear to the log domain

; Input: D = siii iiii | iiii iiii. | 0000 0000 (16TC) in accum A

;

; Outputs:

:

DT.

= 0iii i.fff | ffff 0000 | 0000 0000 (11SM) in accum A

= sXXX XXXX | XXXX XXXX | 0000 0000

DS

(lTC) in Y1

;

MOVE

#$000E, R0

;Get exp bias (14)

MOVE

X:Y_T,B

;Get Y

A A,Yl

;Find DOM=|D|, save DS to Y1

ABS

JNE

<NORMEXP T

;Check for DOM=0

CLR

A (R7) +

; If DOM-0 set DL=0

TMP

<SUBTB T

NORMEXP T

REP

#14

; If DOM!=0, do norm iteration

NORM

R0, A

;14 times to find MSB of DQM

; A1 = 01?? ???? | ???? ???? | 0000 0000 = normalized DQM (A2=A0=0)

; R0 = 0000 0000 | 0000 eeee = exponent of normalized DQM

; Get rid of leading "1" in normalized DQM

; Truncate mantissa to 7 bits and combine with exponent

MOVE

Y:(R7)+,X1

;Get mask K6 ($3F8000)

Y:LSHFT-19,X0

AND

Xl,A

;Truncate MANT, get EXP shift

; A1 = 00mm mmmm | m000 0000 | 0000 0000 (A2=A0=0)

R0.X1

MOVE

;Move EXP to X1

X0,X1,A A,X1 Y:(R7) +,Y0 ;Shift EXP<<19,save MANT to X1,

MPY

;get mask K7 ($100000)

MOVE

A0.A

Move EXP to Al

00mm mmmm | m000 0000 | 0000 0000

; X1=

0eee e000 | 0000 0000 | 0000 0000 (A2=A0=0)

; A1=

MAC Y0,X1,A

;shift MANT>>3 & combine with EXP

; Al= 0eee e.mmm | mmmm 0000 |0000 0000 (A2=A0=0)

= 0iii i.fff | ffff 0000 |0000 0000 (A2=A0=0)

;

Figure 5-4 Linear to Log Conversion Routine

```

The routine ANTILOG in the inverse quantizer performs the opposite conversion. It does so by splitting the exponent and mantissa apart and then shifting the mantissa right again according to the exponent.

#### 5.2.5 Floating-Point Conversion

The other type of conversion required in the ADPCM algorithm is a floating-point conversion. The CCITT specifies that the multiplications in the linear predictor filter be done in a specific floating-point format. After each multiplication, the result must be converted back into fixed-point format before it is accumulated with the other partial products. The data inputs to the predictor filter are the delayed values of  $d_{\alpha}(k)$  and  $s_{r}(k)$ . For each input sample, these values are converted to floating-point and then stored in this form so they do not have to be converted again. The coefficients of the predictor filter a<sub>i</sub>(k) and b<sub>i</sub>(k) are updated in fixed-point form for each sample so they must be converted from linear to floating-point form for each sample. Since there are six zeros and two poles in the predictor filter, the overall requirement is ten fixed-point to floatingpoint conversions and eight floating-point to fixedpoint conversions. Clearly, this conversion process has a major impact on the execution speed of the overall algorithm, so this process must execute as fast as possible. Sixteen of these conversions are performed in the FMULT routine and the other two are performed in the FLOATA and FLOATB routines so that much of the speed emphasis is placed

on the FMULT routine. Again, the overall goal is the minimum worst case execution time.

The floating-point format used in this algorithm consists of four exponent bits, six mantissa bits (with an explicit leading 1), and one sign bit for a total of eleven bits (11FL). As mentioned, the values of  $d_q(k)$  and  $s_r(k)$  are stored in the floating-point format.

```

: FLOATA

:

; Converts the quantized difference signal from 15-bit signed magnitude to

; floating pt. format (llFL - sign, exp, and mant stored separately)

:

; Inputs:

DO = siii iiii | iiii iii.0 | 0000 0000 (15SM) in accum A

;

:

; Outputs:

;

DOO = (11FL)

DOOEXP = X: (R2) = 0000 0000 | 0000 0000 | 0000 eeee

:

DOOMANT = X:(R2+1) = 01mm mmm0 | 0000 0000 | 0000 0000

;

•

DQ05 = X: (R2+2) = SXXX XXXX | XXXX XXXX | 0000 0000

; R2 points to predictor data buffer - DQ0 will overwrite previous SR2

MOVE

X:DQ_T, YO

;Get DOS

Y:DQMAG,A

;Get MAG=DQMAG

MOVE

;Check MAG, get exponent bias (14)

A #$000E,R0

TST

<NORMDQ_T

TNE

;Test MAG

#<$40, A

; If MAG=0 set MANT=100000,

MOVE

MOVE

#0,R0

; and EXP=0

TMP

<TRUNCDO T

NORMDO T

REP

#13

; If MAG!=0 do NORM iteration 13

NORM

R0,A

; times to find MSB of MAG

; Al = 01?? ???? | ???? ???0 | 0000 0000 = normalized MAG (A2=A0=0)

; R0 = 0000 0000 | 0000 eeee = exponent of normalized MAG

TRUNCDO T

MOVE

#<$7E,X0

;Get mask

AND

A,0X

R0,X:(R2)+

;Truncate MANT to 6 bits,

; save EXP to DQLEXP

; Al = 01mm mmm0 | 0000 0000 | 0000 0000 (A2=A0=0)

MOVE

Al,X:(R2)+ ;Save MANT to DQLMANT

MOVE

Y0,X:(R2)+

;Save DQ to DQ1S

```

Figure 5-5 Linear to Floating-Point Conversion Routine

The coefficients do not need to be stored in this format since they are used immediately after they are converted in the FMULT routine. Further details of the FMULT routine are given in the adaptive predictor section, however, a version of FLOATA is shown in Figure 5-5 to illustrate the conversion process. Clearly, the process of normalizing the input value is very similar to that in the logarithmic conversion routine LOG. The main difference is that the sign. exponent, and mantissa components are not combined but are stored separately in the data buffer, using register r2 as a pointer. Note that this storage form was chosen because it requires less data manipulation and shifting. Also notice that the complete value of the two's complement number is stored as the sign. Only the sign of the value is important so the sign does not need to be separated from the rest of the number

#### 5.2.6 Difference Signal Quantization

After the EXPAND conversion routine converts the input signal s(k) to the two's complement signal  $s_l(k)$ , the routine SUBTA subtracts the signal estimate  $s_e(k)$  from this value to form the difference signal d(k). The computation in SUBTA only requires aligning radix points and subtracting. The adaptive quantization of d(k) is not as straightforward. To perform the quantization d(k) must be normalized by the scale factor y(k). As noted previously, the scaling and quantization is performed in base 2 log format. This conversion in the routine LOG is described in **SECTION 5.2.4**.

After conversion the log signal d<sub>i</sub>(k) is scaled in the routine SUBTB and quantized in the routine QUAN. These two routines are shown in Figure 5-6. SUBTB simply truncates the scale factor y(k) and subtracts this value from d<sub>i</sub>(k). then The quantization of this normalized value  $d_{ln}(k)$  in the QUAN routine is done by a table search. The boundary values of the eight quantization regions shown in Table 4-1 are stored in the table QUANTAB in data memory. These values are read from the table using register r0 as a pointer and then compared with  $d_{in}(k)$  until the correct range is found. When the range is found, an offset from the starting address of QUANTAB is subtracted from the last value in r0. This process produces the correct magnitude of I(k) given in Table 4-1.

```

SUBTB

; Scale log version of difference signal by subtracting the scale factor

; DLN = DL - Y

; Inputs:

DL = 0iii i.fff | ffff 0000 | 0000 0000 (llSM) in accum B

Y = 0iii i.fff | ffff ff00 | 0000 0000 (13SM) in accum A

; Output:

DLN = siii i.fff | ffff 0000 | 0000 0000 (12TC) in accum A

*****

SUBTB_T MOVE

Y:(R7),X0

;Get mask K8 ($7FF000)

;Truncate Y to 11 bits (Y>>2)

AND

Х0,В

;Find DLN = DL - Y

SUB

B.A

Figure 5-6 Difference Signal Scaling and Quantization

(sheet 1 of 2)

```

OUAN . Ouantize difference signal in log domain :  $\log 2 |D(k)| - Y(k)$ | |I(k)| : ---- l : 7 [3.12, + inf) : [2.72, 3.12) [2.34, 2.72) 6 : 5 : [1.91, 2.34) 4 : [1.38, 1.91) 3 : [0.62, 1.38]2 : 1 [-0.98, 0.62) . . (-inf, -0.98) 0 ; Inputs: ; DLN = siii i.fff | ffff 0000 | 0000 0000 (12TC) in accum A DS = SXXX XXXX | XXXX XXXX | 0000 0000 (1TC) in reg Yl : ; Output: ; I = siii 0000 | 0000 0000 | 0000 0000 (ADPCM format) in accum A Ouantization table in X memory : ; OUANTAB DC \$F89000 ;-0 98 DC \$050000 ;0 62 : DC \$0B2000 ;1.38 : DC \$0F6000 ;1.91 : \$12C000 DC ;2 34 ; DC \$15D000 ;2.72 ; DC \$190000 ;3.12 : DC \$7FFFFF ;15 99 : ;Get quantization table base ;Get offset for quan. conversion ;Get 1st quan. table value MOVE #OUANTAB, RO MOVE #>OUANTAB+2,X1 MOVE X:(R0)+,X0 TSTDLN T X0, A X:(R0)+, X0 ; Compare to DLN, get next value CMP JGE <TSTDLN\_T ; If value<DLN try next range MOVE R0,A Y:LSHFT-20,X0 ;When range found subtract pointer SUB A, IX ; from base to get IMAG=II ; A1 = 0000 0000 | 0000 0000 | 0000 0iii (A2=A0=0) MOVE Al,X1 MPY X0,X1,A Yl,B ;Shift IMAG <<20, result is ; in A0, move DS into B MOVE A0,A ; A1 = 0iii 0000 | 0000 0000 | 0000 0000 (A2=A0=0) MOVE Al,X:IMAG ;Save IMAG A #<\$F0,X0 ;Check IMAG, get invert mask TST <INVERT\_T ; If IMAG=0 invert bits JEQ ; else check DS TST В JPL <IOUT T ; If DS=1 don't invert IMAG ; If DS=0 or IMAG=0 invert IMAG INVERT\_T EOR X0,A ;Adjust sign extension IOUT T MOVE Al,A

Figure 5-6 Difference Signal Scaling and Quantization (sheet 2 of 2)

The magnitude of I(k) is shifted to the MSBs of register a1 and is then combined with the sign value  $d_{c}(k)$  which was previously saved in register v1 in the LOG routine. The ADPCM word I(k) is in a sign magnitude type format. If  $d_{s}(k)$  is negative then the four MSBs of the accumulator are inverted, setting the sign bit to 1 and inverting the magnitude bits. If the sign is positive the magnitude of I(k) is not changed leaving the sign set to 0. A special case occurs when the magnitude of I(k) is 0. In this case the bits are inverted even if the sign is positive. This means that an all zero word is not legal and will never be transmitted. This is why the quantizer is referred to as a 15-level quantizer. It should be noted however that transmission errors can cause an all zero word to be received by the decoder so this case must be taken into account in the inverse quantization.

#### 5.2.7 Inverse Quantization

The inverse quantization of the ADPCM sample I(k) is performed in the routines RECONST and ADDA. These routines are shown in Figure 5-7. The RECONST routine uses a table lookup to find  $d_{Inq}(k)$  — the quantized version of  $d_{In}(k)$ . After removing the sign of I(k) the magnitude is inverted if necessary and is then shifted to the three LSBs of the 24-bit word. This magnitude is then moved to the offset register n4 where it is used as an offset to find one of eight values stored in the lookup table IQUANTAB (defined in Table 4-1). The scale factor y(k) is added to the result to find the denormalized value  $d_{ql}(k)$ .

```

:

RECONST

:

; Reconstruct quantized difference signal in the log domain

:

|\log_2 |DQ(k)| - Y(k)

:

[I(K)]

;

7

3.32

:

2 91

:

6

5

2.52

:

4

:

2.13

٦

1.66

:

2

1.05

;

:

1

0.031

- inf

:

Ο

;

; Inputs:

I = iiii 0000 | 0000 0000 | 0000 0000 (ADPCM format) in accum A

:

:

; Output:

DOLN = siii i.fff | ffff 0000 | 0000 0000 (12TC) in accum A

:

DOS = SXXX 0000 | 0000 0000 | 0000 0000 (1TC) in reg Y1

:

:

:

; Inverse quantization table in X memory

:

DC

$800000

;-16

; TOUANTAB

|T| = 0

;

DC $004000

;0.031

|I|=1

$087000

:

DC

;1.05

|I|=2

DC

T = 3

;

$0D5000

;1.66

|I|=4

;

DC

$111000

;2.13

;2.52

|T|=5

:

DC

$143000

DC $175000

;2.91

|T|=6

;

;

DC $1A9000

;3.32

|I|=7

#<$F0.X1

MOVE

;Save DOS (sign of I) to Y1

MOVE

A,Y1

A,X:I R

EOR

Xl,A

Y:RSHFT+20,Y0

;Invert bits of I

; If ^IS=1 use I, else use ^I

TMT

A. [Y

; A1 = 0iii 0000 | 0000 0000 | 0000 0000

MOVE

Al,XO

MOVE

Al,X:IMAG

;Save |I|

;shift IMAG>>20

MPY

X0,Y0,A #IOUANTAB,R4

; A1 = 0000 0000 | 0000 0000 | 0000 0iii (A2=A0=0)

MOVE

Al.N4

;Load IMAG as offset into IQUAN table

MOVE

X:Y R,B

;Get Y

MOVE

X:(R4+N4),A

;Lookup DOLN

Figure 5-7 Inverse Quantization and Scaling of ADPCM Codeword

(sheet 1 of 2)

```

```

• *

גממא

; Add scale factor to log version of guantized difference signal

; DOL = DOLN + Y

; Inputs:

Y = 0iii i.fff | ffff ff00 | 0000 0000 (13SM) in accum B

DOLN = siii i.fff | ffff 0000 | 0000 0000 (12TC) in accum A

; Output:

DOL = siii i.fff | ffff 0000 | 0000 0000 (12TC) in accum A

•

MOVE

Y:(R7)+,Y0 ;Get mask K8 ($7FF000)

ΔND

Y0.B

;Truncate Y to 11 bits (Y<<2)

;Find DQL=DQLN+(Y<<2)

B.A

Figure 5-7 Inverse Quantization and Scaling of ADPCM Codeword

```

This logarithmic value is converted back into linear form in the routine ANTILOG to find the result of the overall inverse quantization procedure  $d_q(k)$ , the quantized version of the difference signal.

The quantization and inverse quantization procedures can serve as illustrations of one way of implementing an adaptive quantization in a waveform coder. The adaptation of y(k), discussed in **SECTION 5.2.10**, addresses the adaptive characteristic of the scale factor but the scaling and quantization process described here can still be used no matter how the adaptation is performed.

#### 5.2.8 Adaptive Predictor

The adaptive predictor portion of the ADPCM algorithm is implemented in two main sections. The

(sheet 2 of 2)

first section is the prediction filter itself, shown in Figure 4-5. This section consists of the routines FMULT and ACCUM. The filter uses delayed data and coefficient values so FMULT and ACCUM are the first two routines executed in the encoder and the decoder. The second section consists of the reconstructed signal calculation and the adaptation of the predictor coefficients. These routines are executed after the inverse quantization in both the encoder and the decoder.

The adaptive predictor is the most computationally intensive portion of the ADPCM implementation on the DSP56001. One of the main reasons for this is the floating-point multiplies that are required in the FMULT routine, as was discussed in the floatingpoint conversion section. The FMULT routine is set up as a hardware DO loop that is executed eight times, two for the poles and six for the zeros. For each tap of the filter the two's-complement coefficient must be converted to the floating-point format before it is multiplied with the delayed data value. After the multiplication each partial product must be converted to the fixed point format. Overall eight fixed-point to floating-point conversions and eight floating-point to fixed point conversions are required in the FMULT routine. The flow description within each loop of FMULT is as follows:

- 1. Convert the 16-bit two's complement coefficient to a 13-bit magnitude and a 1-bit sign.

- 2. Convert the 13-bit magnitude to a 4-bit exponent and a 6-bit mantissa.

- 3. Add the exponents of the coefficient and the data to find the 5-bit exponent of the partial product.

- 4. Multiply the mantissas of the coefficient and the data and truncate the results to find the 8-bit mantissa of the partial product.

- 5. Convert the exponent and the mantissa of the partial product to a 15-bit magnitude.

- 6. Exclusive-OR the signs of the coefficient and the data to find the sign of the partial product.

- Convert the 15-bit magnitude and 1-bit sign of the partial product to a 16-bit two's complement number.